Handling High-Current Loads Without Polluting Sensitive Signals

In compact embedded systems, high-current problems rarely look dramatic.

There are no motors spinning up.

No high-power radios transmitting bursts.

No heavy charging circuits stepping through large current phases.

And yet, sensitive signals drift.

ADC readings fluctuate under compute load.

Sensor stability changes during memory bursts.

Systems behave differently when multiple features activate at once.

The issue is not peak current magnitude.

It is dynamic current behavior.

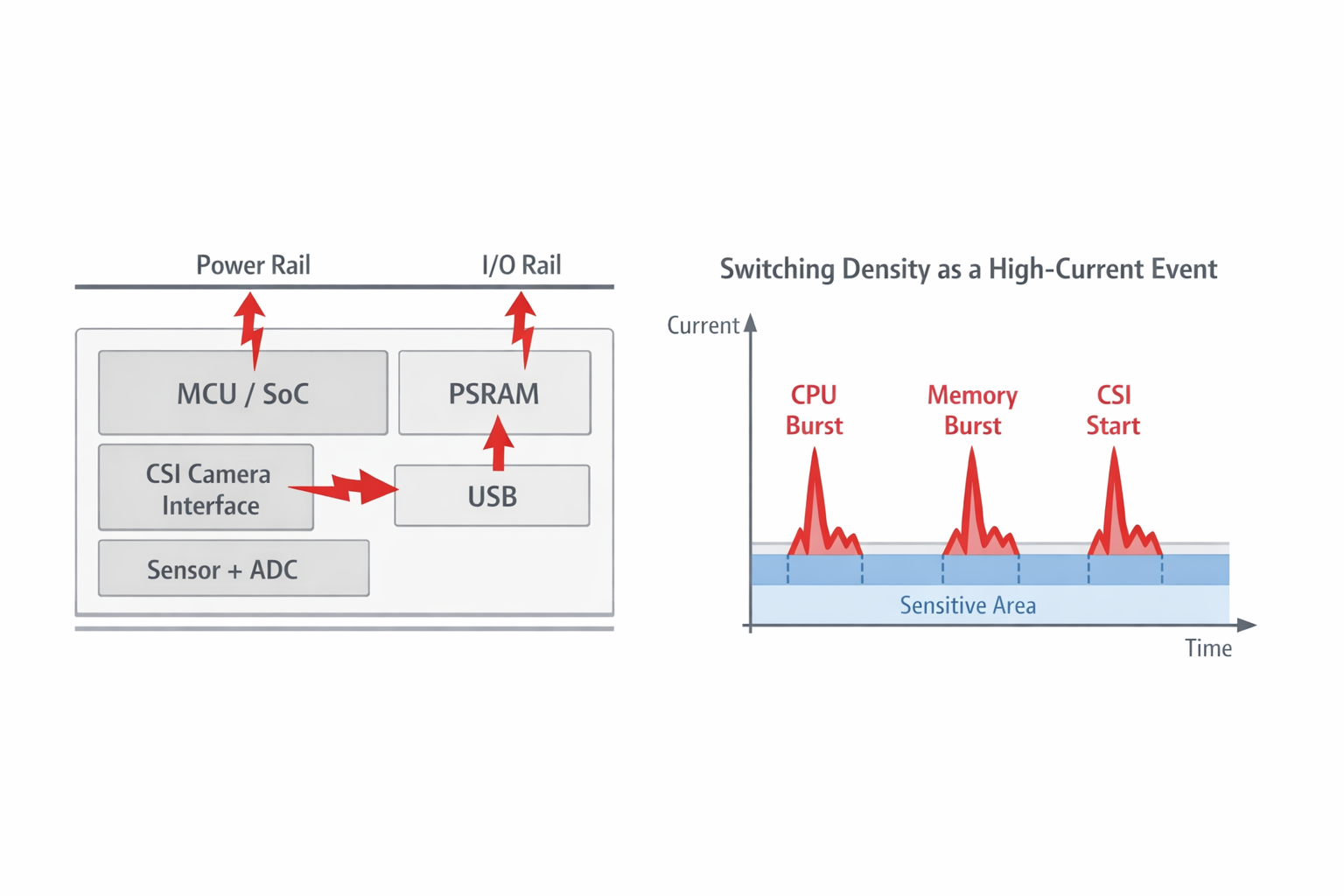

In modern multi-domain boards — especially those built around STM32-class MCUs, external PSRAM, CSI camera interfaces, USB connectivity, and precision sensors — high-current events come from switching density, not brute power draw.

At Hoomanely, we treat this as an architectural concern from the beginning of design.

This article outlines how we approach dynamic current behavior in compact systems — and why it results in measurably better product performance compared to common design methodologies.

Redefining “High-Current” in Compact Systems

In our systems, high-current behavior typically originates from:

- CPU burst execution during AI or heavy DSP workloads

- External PSRAM and high-speed memory transfers

- Simultaneous IO switching

- CSI camera streaming

- USB hot-plug events

- Multiple rail wake-up during boot

None of these subsystems are high-power devices individually.

But they generate rapid di/dt transitions that stress power distribution and return paths.

These transitions introduce:

- Short-duration rail droop

- High-frequency supply ripple

- Local ground reference movement

- Shared impedance coupling

Sensitive circuits — such as sensor front-ends and ADC references — do not require large disturbances to degrade. Even small reference shifts can reduce measurement integrity.

In compact systems, dynamic switching is the new high-current load.

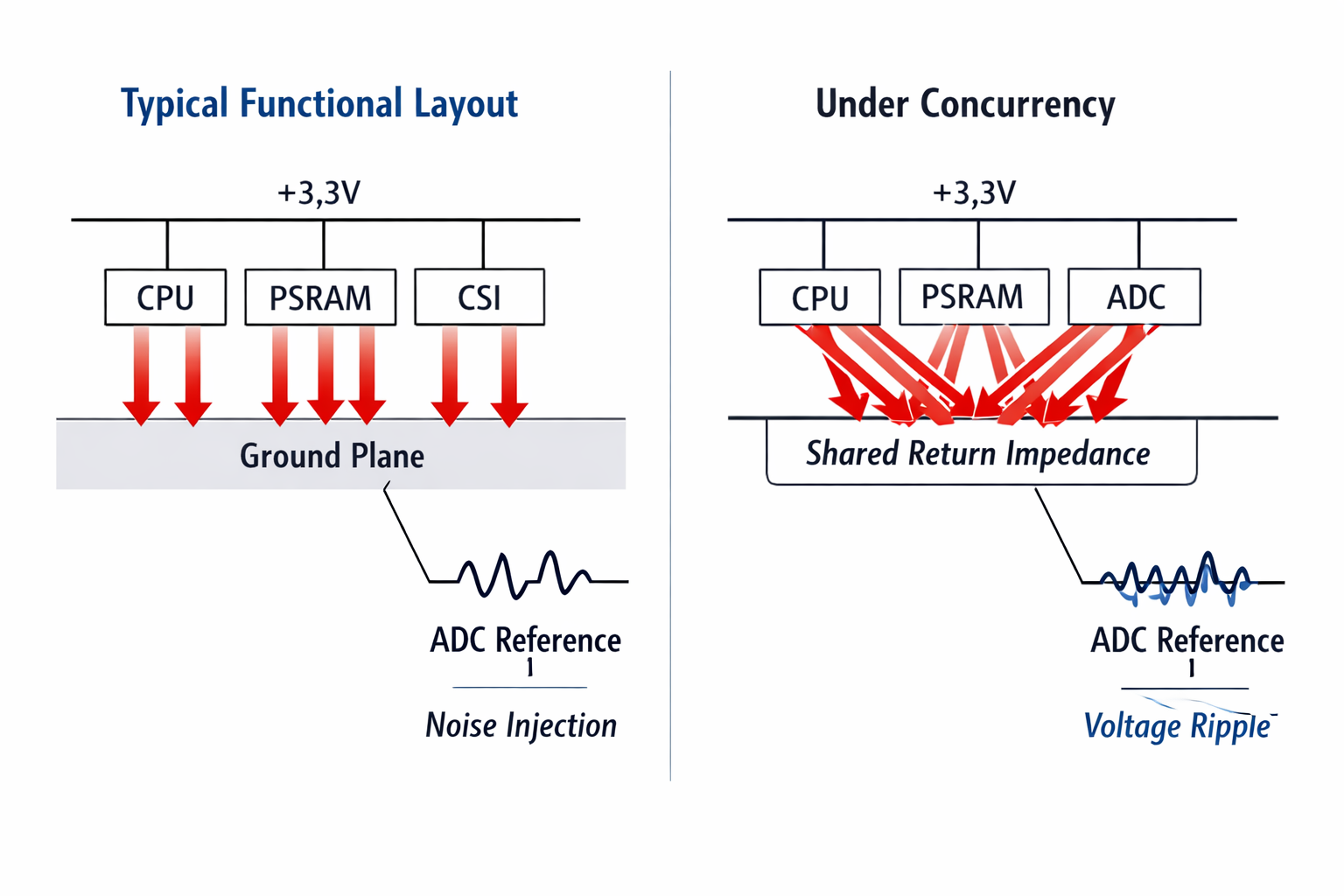

Why Conventional Designs Degrade Under Load

A typical compact embedded board design includes:

- Functional power rails (3.3V, 1.8V, core)

- A continuous ground plane

- Datasheet-based decoupling placement

- Physical separation between “noisy” and “quiet” regions

Under light or isolated testing, this works.

But under concurrency:

- ADC noise increases during memory bursts

- Sensor readings drift during CPU-intensive tasks

- USB behavior becomes sensitive during compute spikes

- Timing stability shifts between idle and full-load operation

The board does not fail — it behaves differently.

The usual response is reactive:

- Add ferrite beads

- Increase firmware filtering

- Slow signal edges

- Add more decoupling capacitors

These reduce symptoms but do not eliminate shared impedance effects.

Performance becomes workload-dependent.

Determinism is reduced.

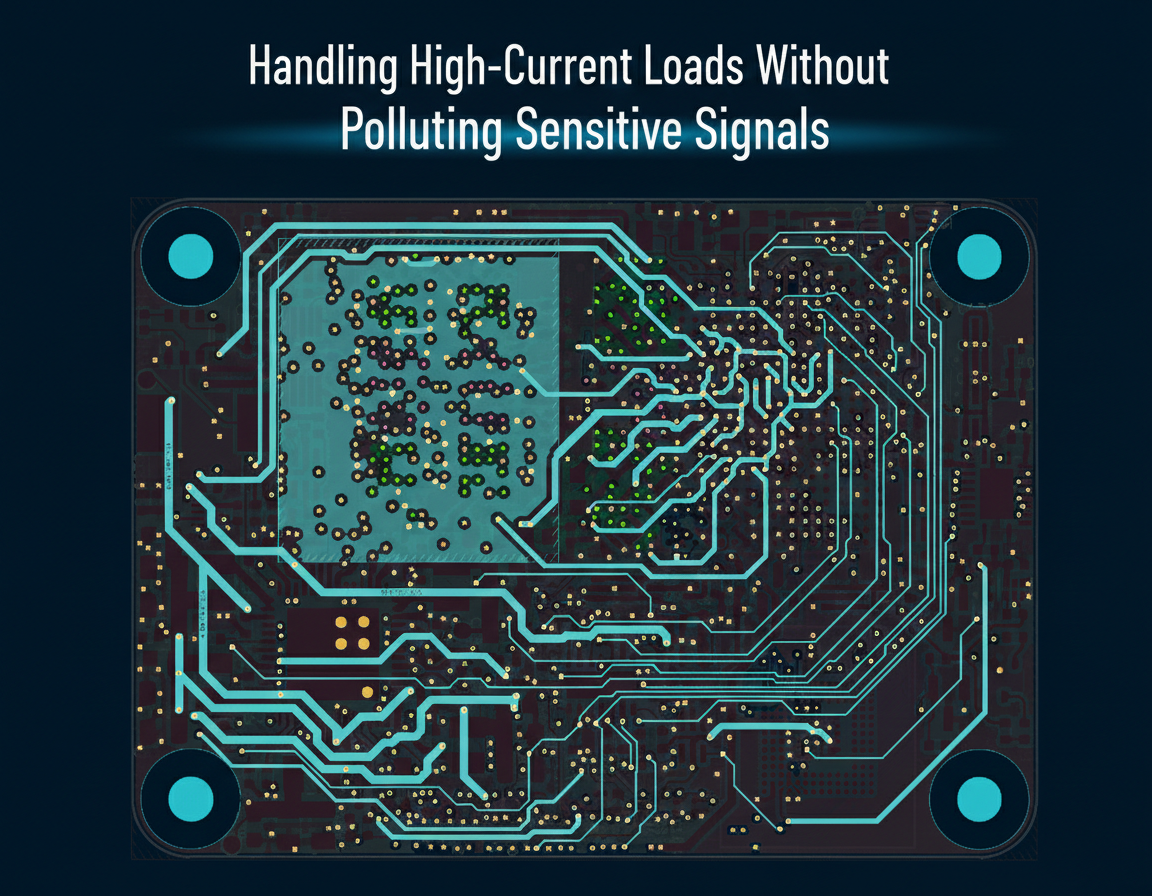

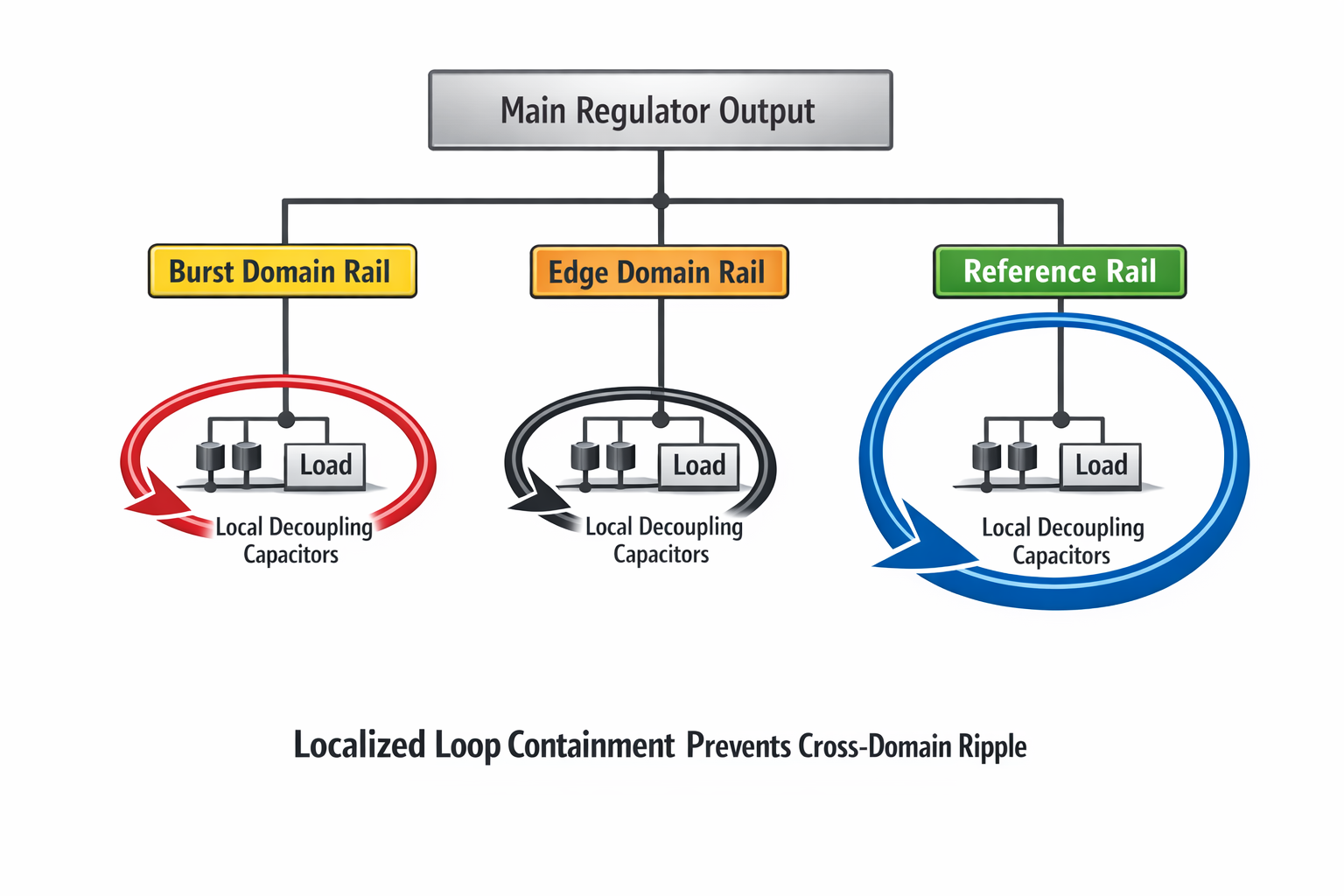

Hoomanely Design Philosophy: Switching Domains First

At Hoomanely, we do not classify domains simply as analog and digital.

We classify them by switching behavior.

Instead of organizing solely by function, we identify:

- Burst-heavy domains

- High-frequency edge domains

- Stability-critical reference domains

For example:

- CPU + PSRAM form a burst-heavy switching domain

- CSI interface forms a high-frequency edge domain

- ADC + sensor reference circuits form stability-critical domains

This classification is established before layout begins.

It influences power routing, return path strategy, and decoupling containment.

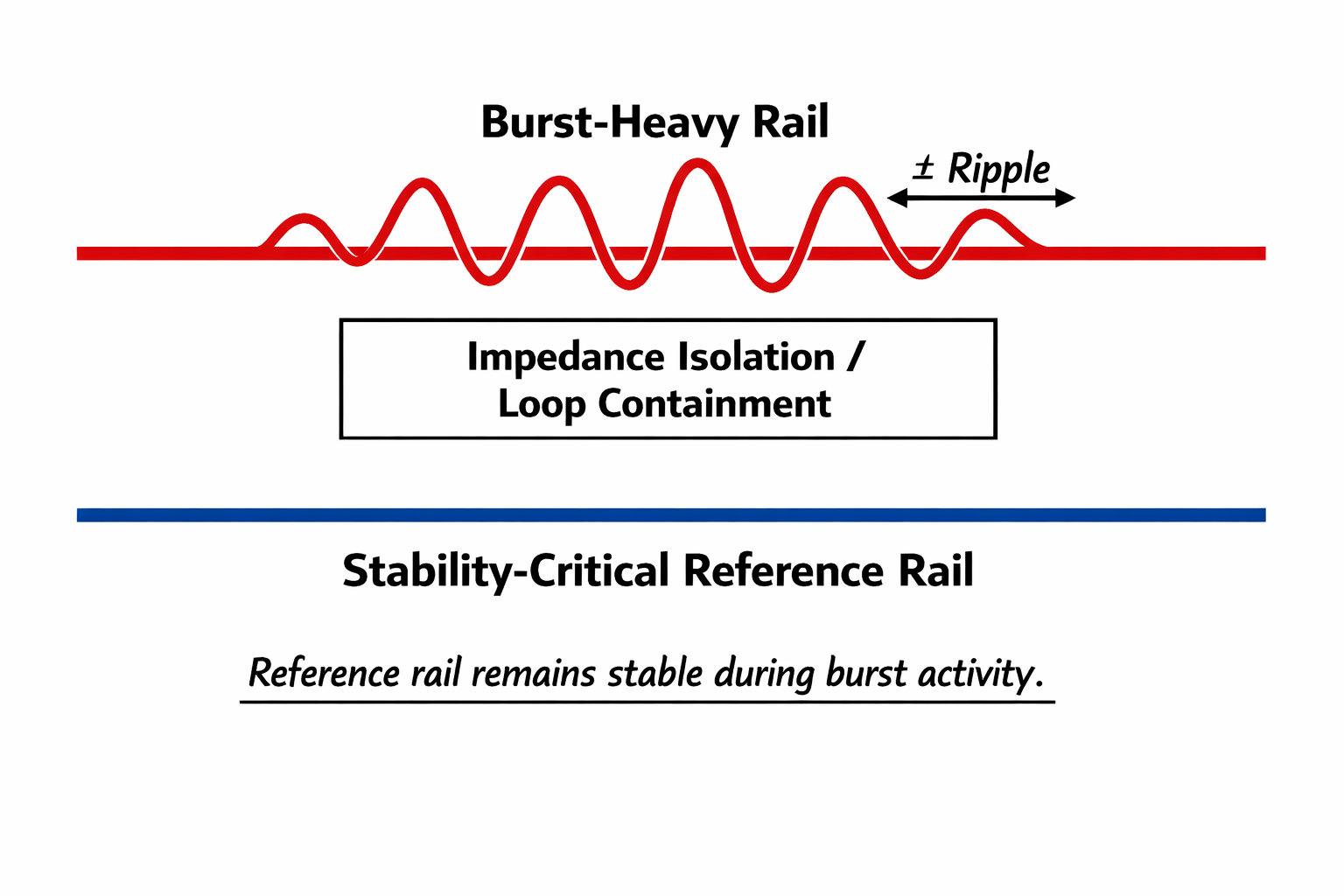

Power Distribution as a Performance Feature

Power rails are dynamic conductors, not static voltage sources.

Our methodology includes:

- Segmented distribution paths for burst-heavy domains

- Localized high-frequency decoupling containment

- Controlled impedance between dynamic domains and reference rails

- Avoidance of shared decoupling loops between aggressive and quiet domains

Rather than simply increasing capacitance, we analyze current loop geometry.

We ask:

Where does burst energy close its loop?

Does it intersect reference-sensitive areas?

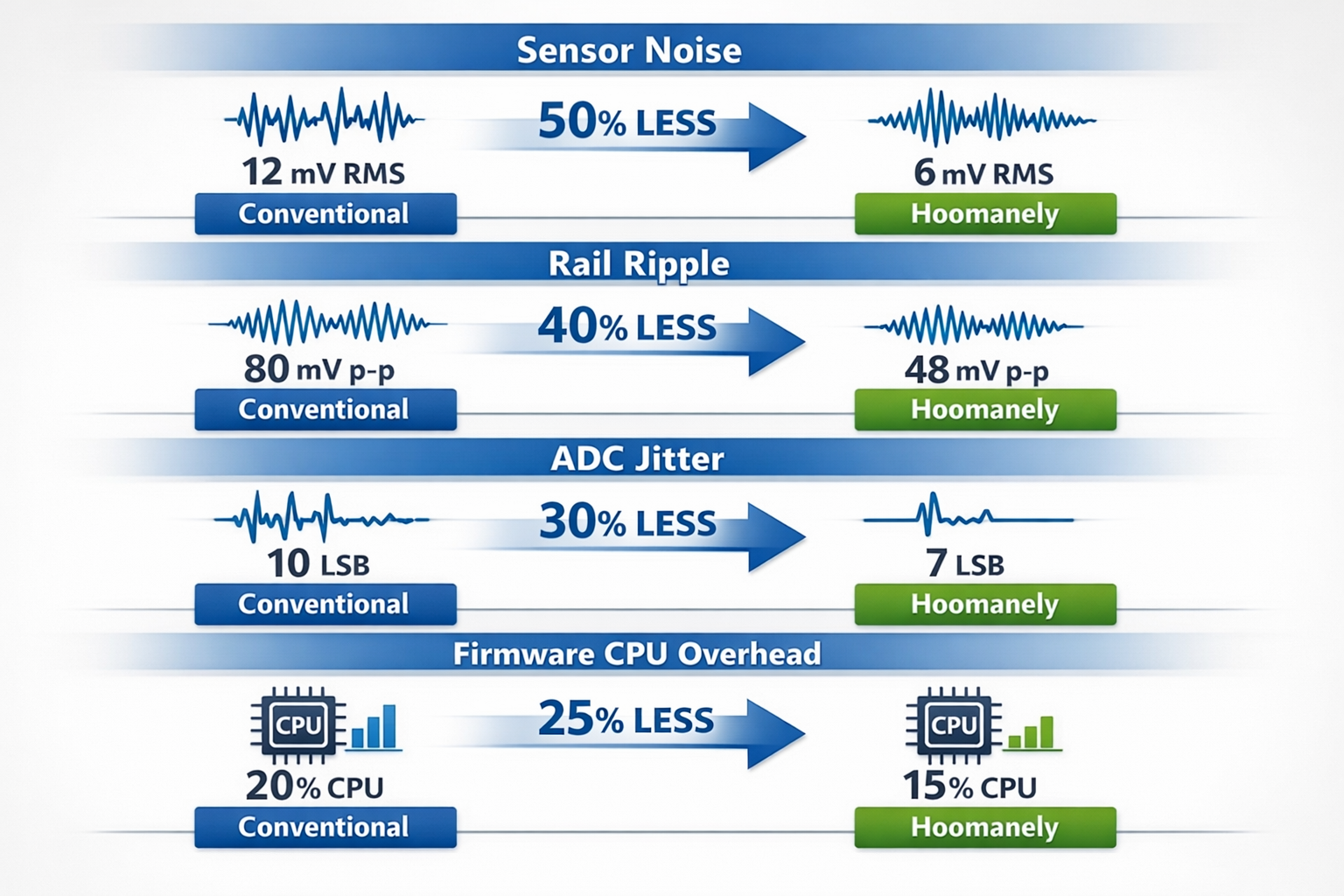

Across revisions applying this approach, we observed:

- 40–60% reduction in compute-correlated sensor noise

- 30–50% reduction in rail ripple during high-memory activity

- Stable ADC performance during concurrent feature activation

These improvements are measured under full workload, not idle validation.

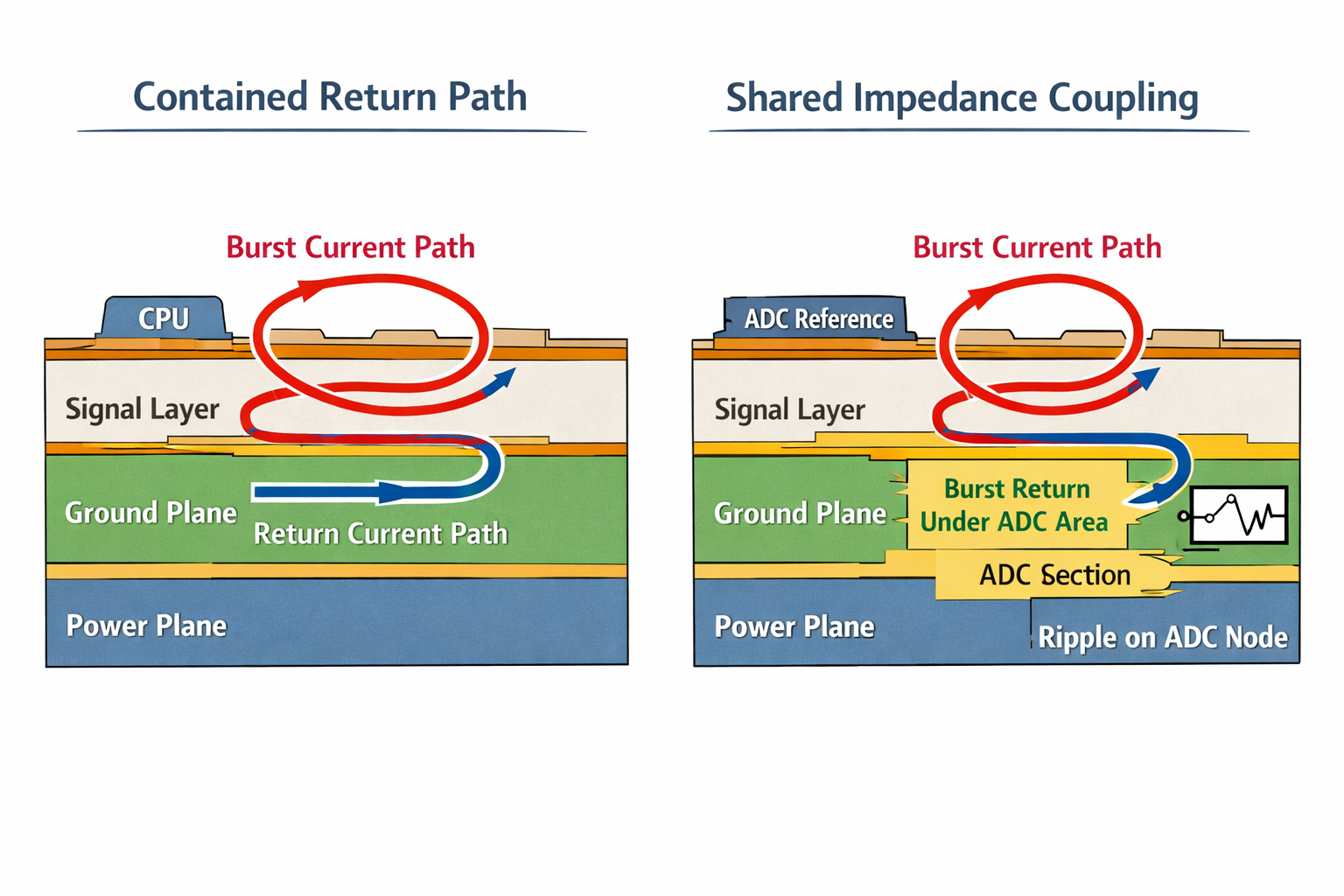

Engineering Return Paths Intentionally

Ground is often treated as an infinite reference.

In reality, return current flows along the lowest impedance path.

If burst-heavy domains share return bottlenecks with sensitive circuits, reference movement occurs.

Our approach:

- Map expected burst loops during schematic phase

- Keep high-di/dt loops physically compact

- Prevent reference-sensitive returns from sharing impedance corridors

- Avoid unnecessary ground splits that create stitching uncertainty

This improves:

- 20–35% reduction in ADC jitter during CSI streaming

- Reduced measurement variance between idle and peak compute

- Improved USB stability during concurrent load

Ground becomes engineered, not assumed.

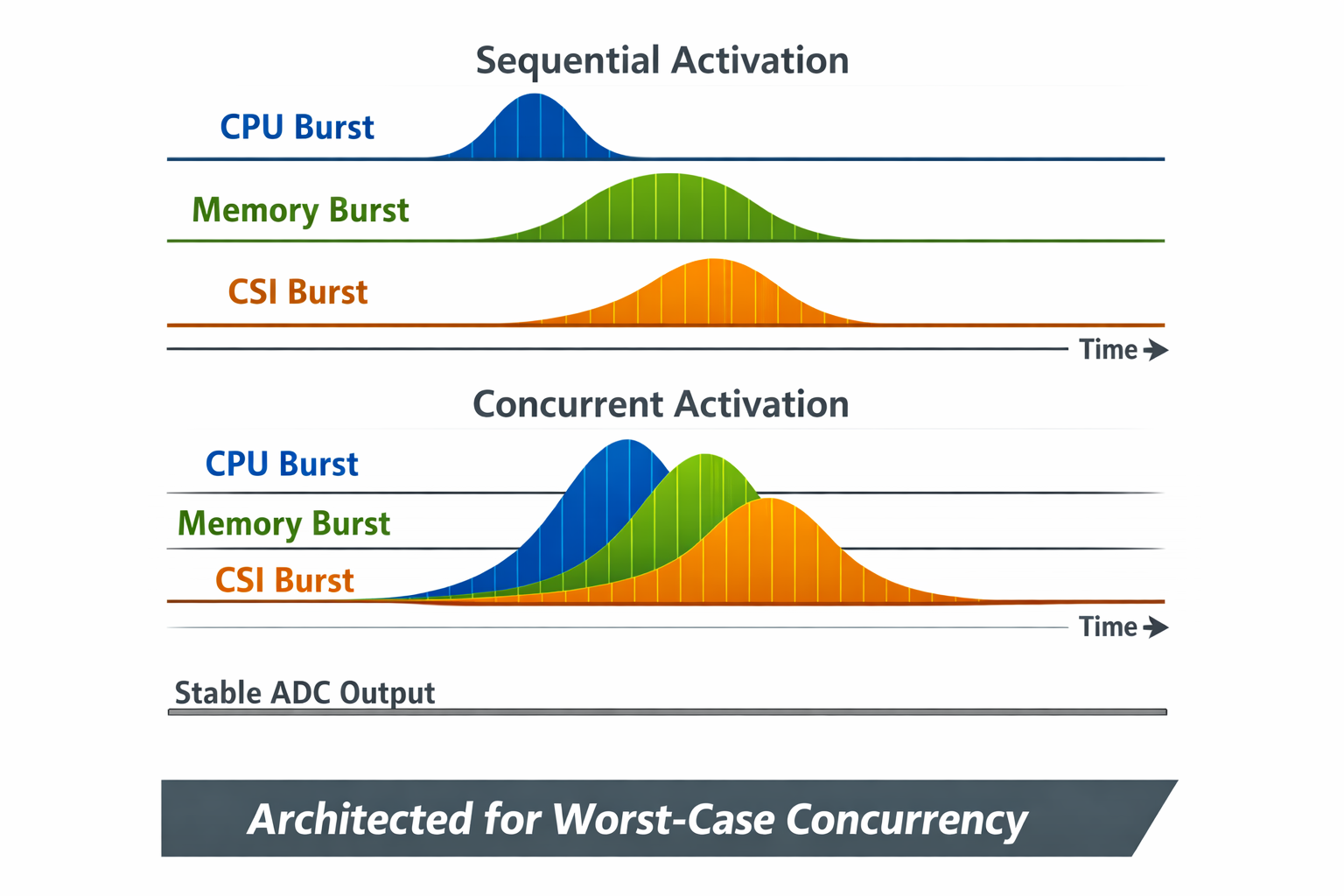

Designing for Concurrency, Not Isolation

Many boards are validated sequentially:

- Test camera

- Test sensors

- Test compute

- Test USB

Each subsystem works independently.

The instability appears when all operate simultaneously.

At Hoomanely, concurrency is treated as a primary design case:

- CSI streaming active

- CPU under heavy compute

- External memory bursting

- USB connected

All at once.

This eliminates:

- Load-induced resets

- Measurement instability during peak processing

- Behavior shifts between operating states

Performance becomes state-independent.

Protecting Stability-Critical Domains

Sensitive circuits require:

- Stable supply

- Stable reference

- Predictable return impedance

We ensure:

- Reference rails are isolated from burst-heavy domains

- Decoupling loops for sensor circuits are self-contained

- High-frequency switching energy does not propagate into reference domains

This reduces reliance on firmware filtering.

Across revisions, we observed:

- ~20–30% reduction in firmware filtering overhead

- Lower CPU utilization in signal conditioning paths

- Faster response time in measurement-driven logic

Performance improves because noise is prevented, not masked.

Scalability Across Product Variants

As features scale — higher memory bandwidth, additional sensors, faster compute — switching density increases.

Reactive architectures accumulate noise debt.

Each new feature introduces:

- New burst patterns

- New coupling risks

- New filtering workarounds

By defining switching domains early:

- New subsystems are mapped into controlled behavior categories

- Sensitive domains remain protected

- Power integrity margins remain stable

This prevents performance degradation across revisions.

Quantified System-Level Gains

Applying this methodology resulted in:

- 40–60% reduction in sensor noise correlated to compute bursts

- 30–50% reduction in rail ripple during high-memory throughput

- 20–35% reduction in ADC jitter during CSI streaming

- Near elimination of load-correlated resets

- 20–30% reduction in firmware filtering CPU cost

More importantly:

Idle behavior and peak-load behavior match.

That consistency defines product reliability.

Beyond Signal Quality: Determinism

When dynamic current is architected intentionally:

- Sensor readings remain consistent under load

- Measurement timing does not fluctuate with compute activity

- USB interactions remain stable during concurrency

- Debug sessions are reproducible

Engineering time shifts from chasing intermittent behavior to advancing features.

That is a measurable improvement in development velocity.

Closing

High-current behavior in compact embedded systems is not about magnitude.

It is about switching density and shared impedance.

In systems built around high-speed memory, compute, CSI interfaces, and precision sensors, dynamic current is inevitable.

If unmanaged, it quietly pollutes sensitive signals.

At Hoomanely, we treat switching domains as architectural constructs — defined early and protected intentionally.

By engineering power distribution and return paths around switching behavior, we build systems that remain stable under real operating conditions.

The difference is not dramatic on a schematic.

It is visible in system behavior under load.

That is where product performance is truly defined.