Making Sensor Power-Up Order Enforceable in Hardware

In embedded sensor systems, the difference between a stable product and a fragile one often comes down to something that users never see:

The order in which sensors wake up.

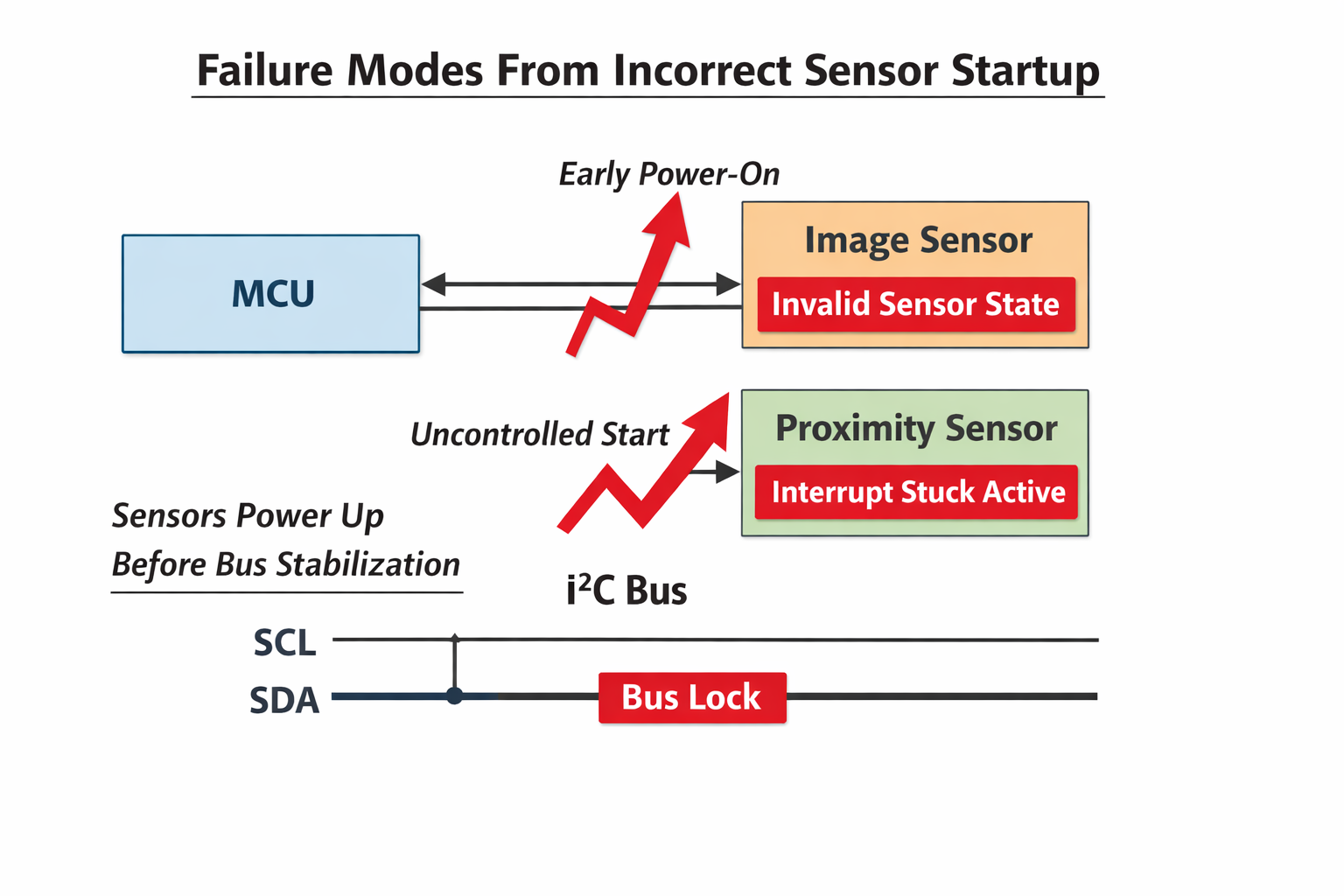

It may sound like a small detail. But in multi-sensor platforms — where image sensors, proximity sensors, microcontrollers, and communication interfaces all share power domains and buses — startup order determines whether the system behaves predictably.

If the sequence is wrong, the result is rarely a catastrophic failure.

Instead, it becomes something far worse: intermittent instability.

A sensor that fails once every few hundred boots.

An I²C bus that occasionally hangs during startup.

A camera that initializes correctly most of the time, but not always.

Those issues are not software bugs. They are sequencing problems.

At Hoomanely, we stopped treating sensor startup orders as a firmware responsibility. Instead, we enforce it directly in hardware, so that the system behaves correctly even before firmware runs.

Why Sensor Power-Up Order Matters

Most sensors are not purely digital devices. Internally, they contain:

- Analogue bias generators

- Clock generators

- Internal state machines

- Calibration memory

- Mixed-signal interfaces

These subsystems assume a defined power-up sequence.

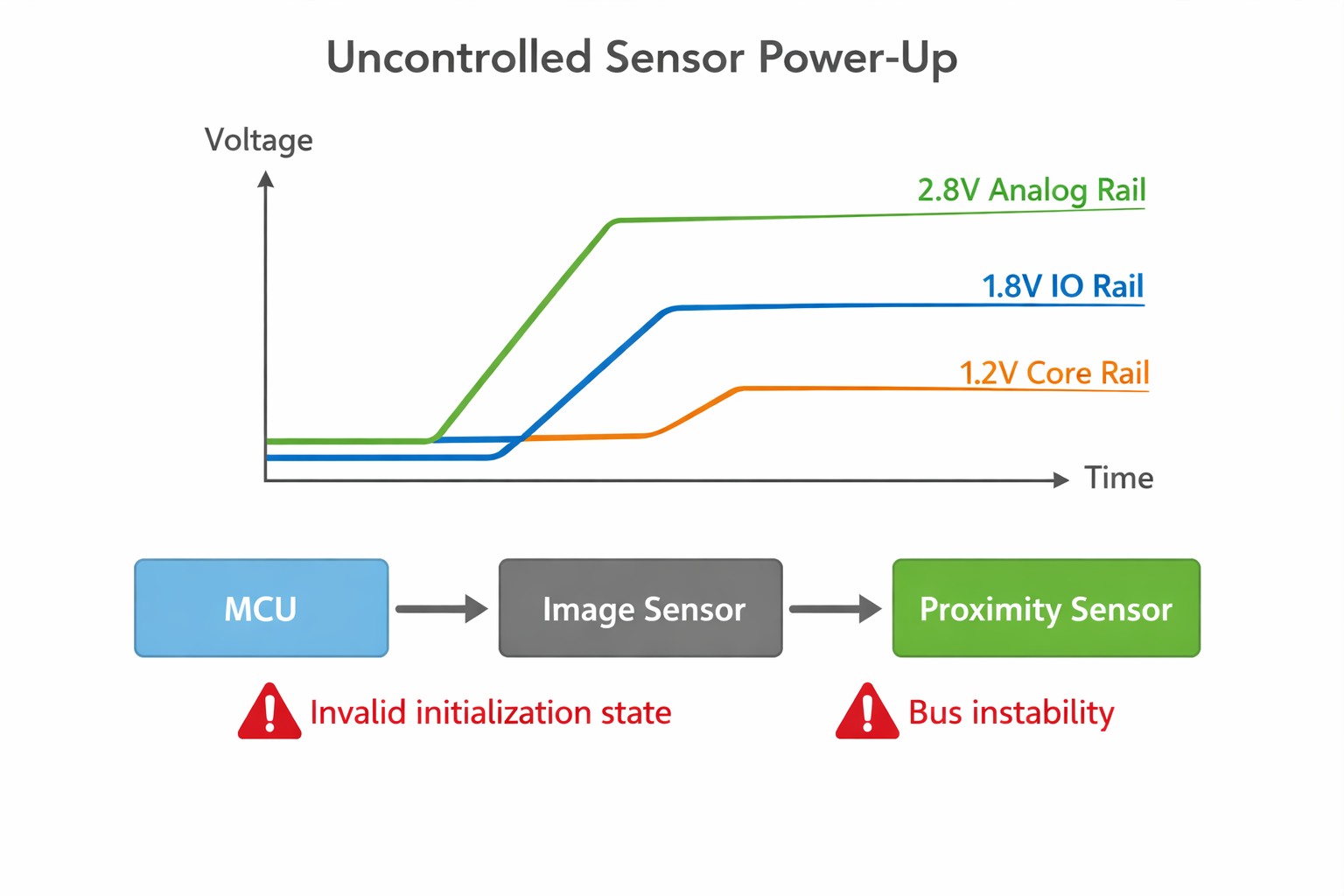

For example, an image sensor typically requires:

- Analog rail stabilization

- IO rail stabilization

- Core logic rail activation

- Clock availability

- Reset release

If those events occur out of order, the sensor may:

- Latch an invalid internal state

- Enter a diagnostic mode

- Fail to respond on the bus

- Generate unstable output

The problem is that many systems leave these dependencies to chance.

The Common Approach: Let Firmware Handle It

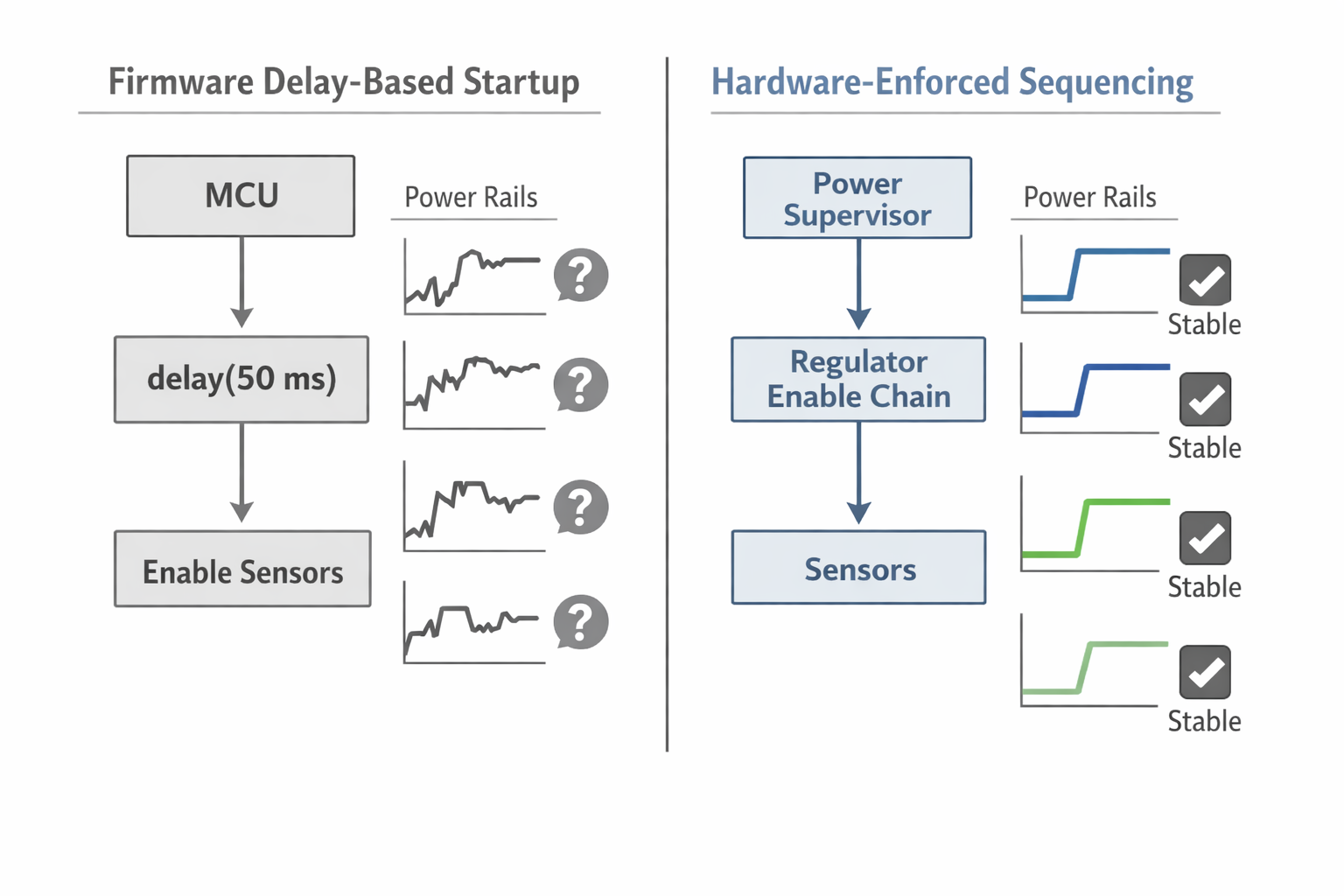

In many designs, the sensor startup flow looks like this:

- Power rails enable together

- MCU boots

- Firmware delays for a few milliseconds

- Sensors are initialised sequentially

This approach works under ideal conditions.

But it assumes several things that are not guaranteed:

- Rails reach stable voltage at the same rate

- Sensors complete internal power-on reset within expected time

- Bus lines remain stable during the ramp

- IO pins do not inject current into partially powered domains

In practice, these assumptions are fragile.

Even small changes in temperature, power supply ramp rate, or component tolerance can alter startup timing enough to trigger intermittent behaviour.

Hardware Sequencing Removes Guesswork

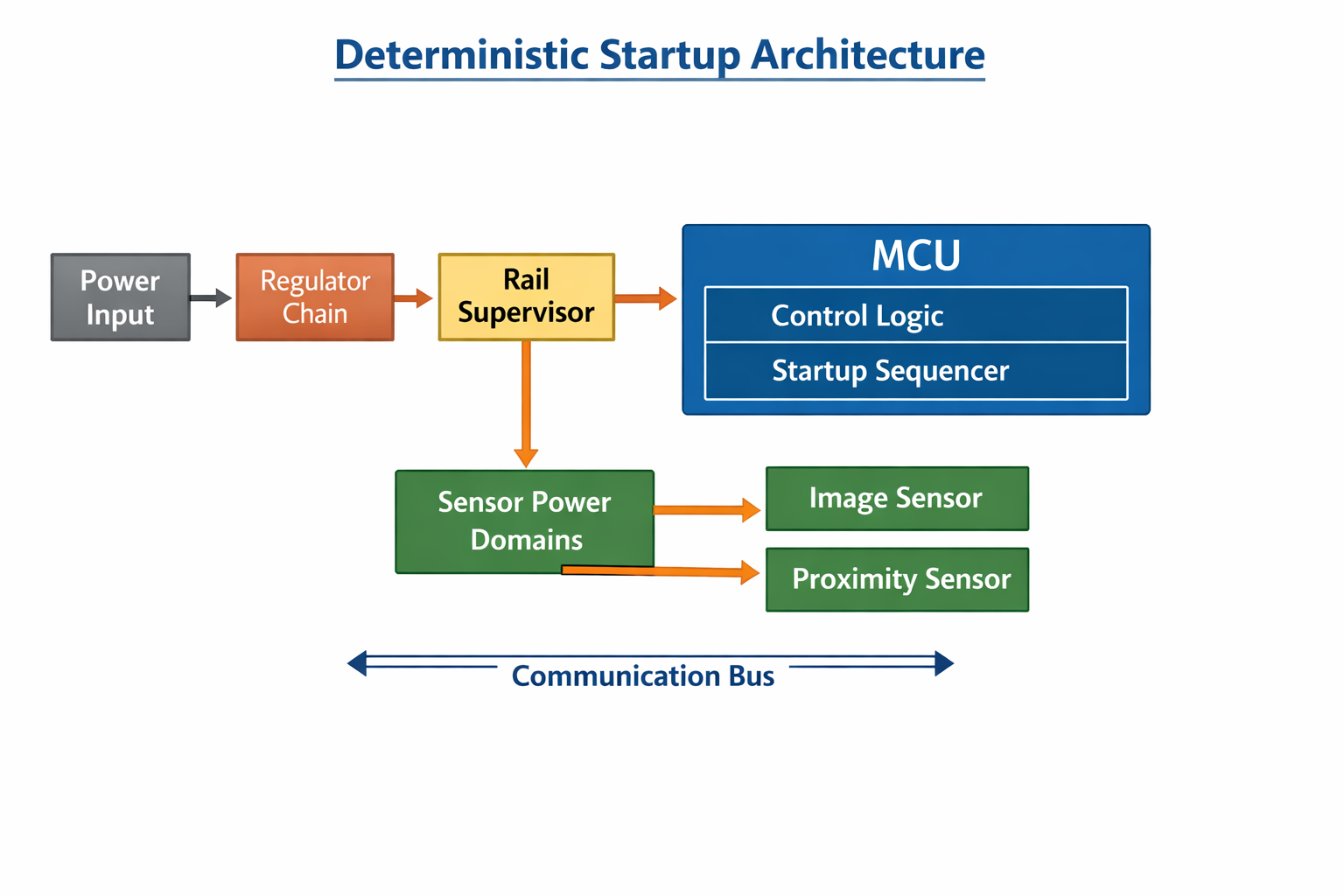

Instead of relying on firmware delays, we design the system so that sensor power-up order is physically enforced.

This means that each stage of the system must reach a valid electrical state before the next stage is allowed to start.

Typical enforcement mechanisms include:

- Regulator enable chaining

- Power supervisors

- Reset gating

- Sensor shutdown pins

Each element ensures that the next subsystem cannot start prematurely.

As a result, the sequence becomes deterministic.

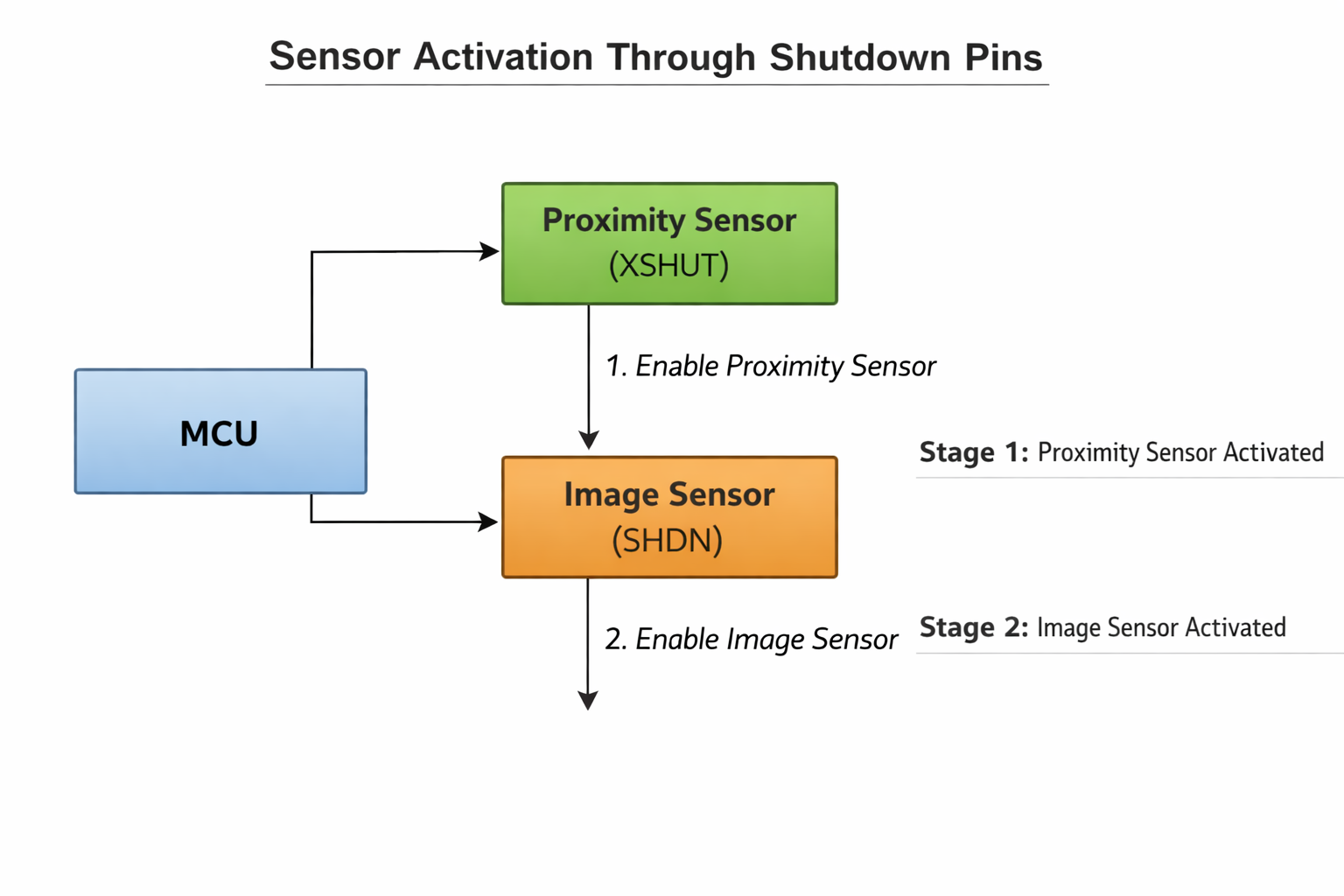

Using Shutdown Pins as Hardware Control Points

Many sensors include a shutdown or enable pin.

This pin is often treated as a simple GPIO controlled by firmware.

Instead, we use it as a hardware sequencing element.

For example:

- Power rails stabilise

- MCU completes basic initialisation

- Firmware configures clocks and buses

- Sensor shutdown pins are released in a defined order

But the important detail is that these pins remain inactive until the hardware power tree is already stable.

This ensures that sensors never attempt to initialise in a partially powered system.

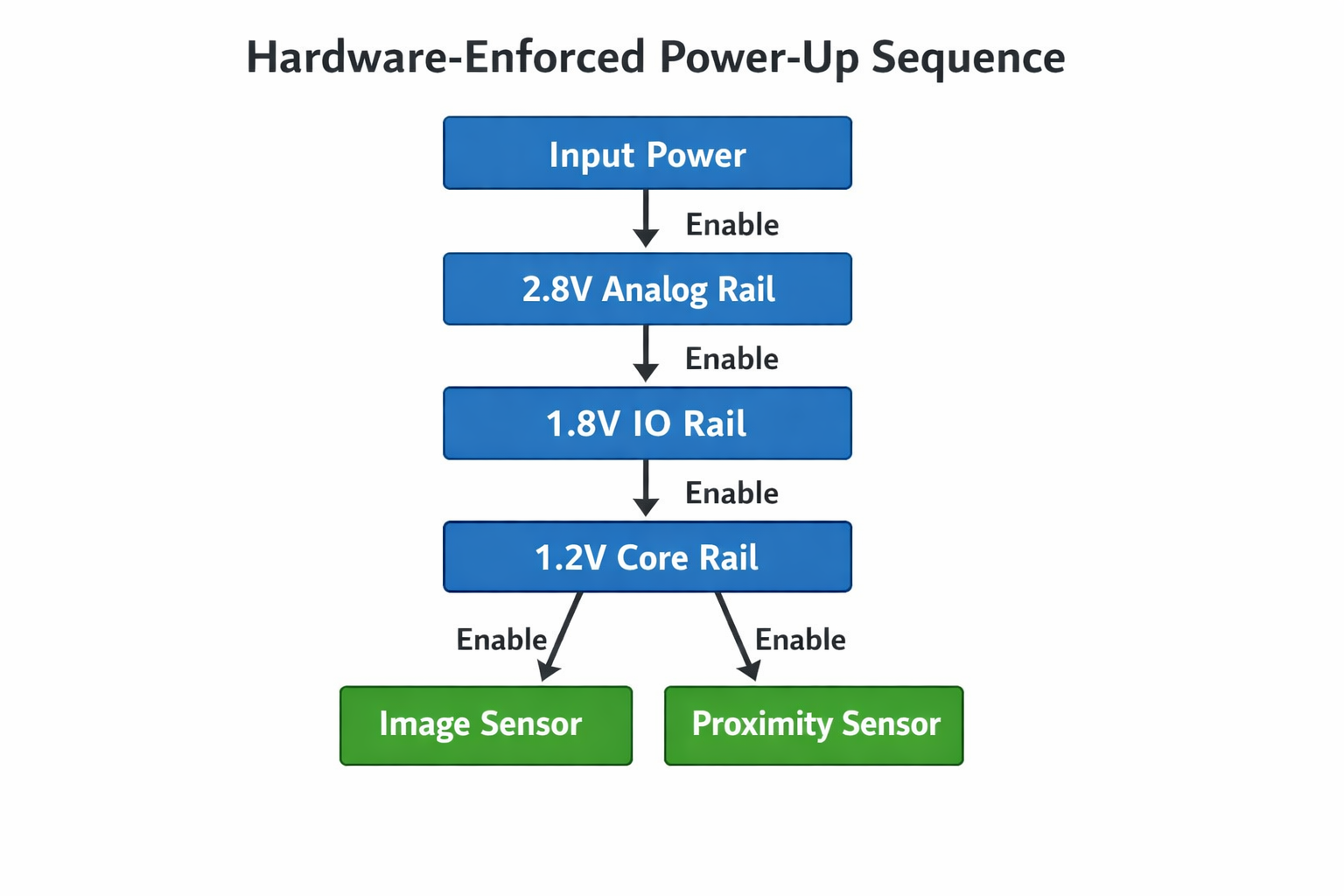

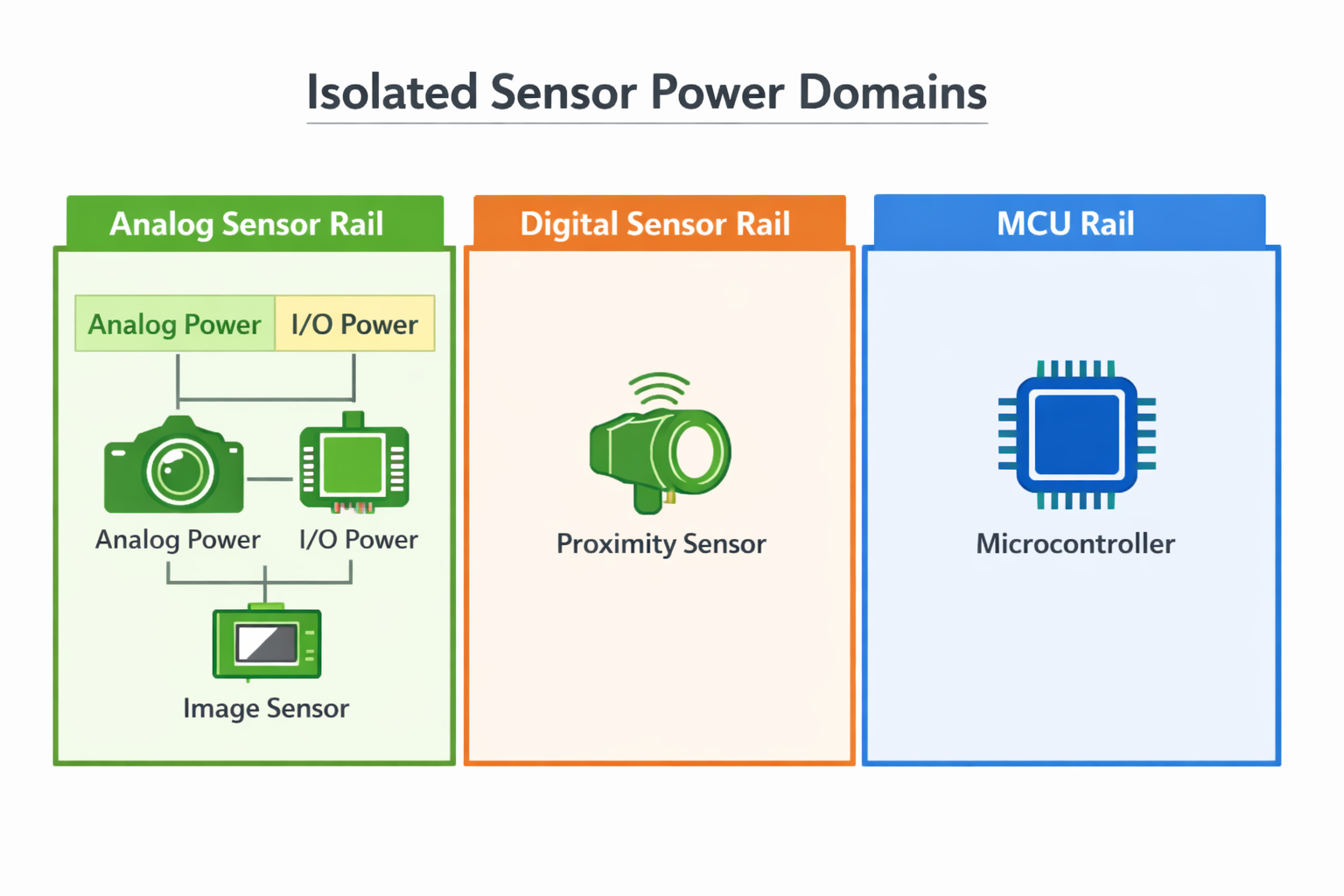

Separating Power Domains for Sensors

Another key technique is isolating sensor power domains.

Instead of sharing the same rail across multiple sensors, we create controlled domain boundaries.

This provides several benefits:

- Individual sensors can be enabled sequentially

- Faulty devices cannot disturb other sensors

- Analogue rails remain clean during digital ramp events

For example, an image sensor may have:

- Analog rail

- IO rail

- Core rail

While proximity sensors may share a separate controlled rail.

This separation allows us to bring up devices one stage at a time.

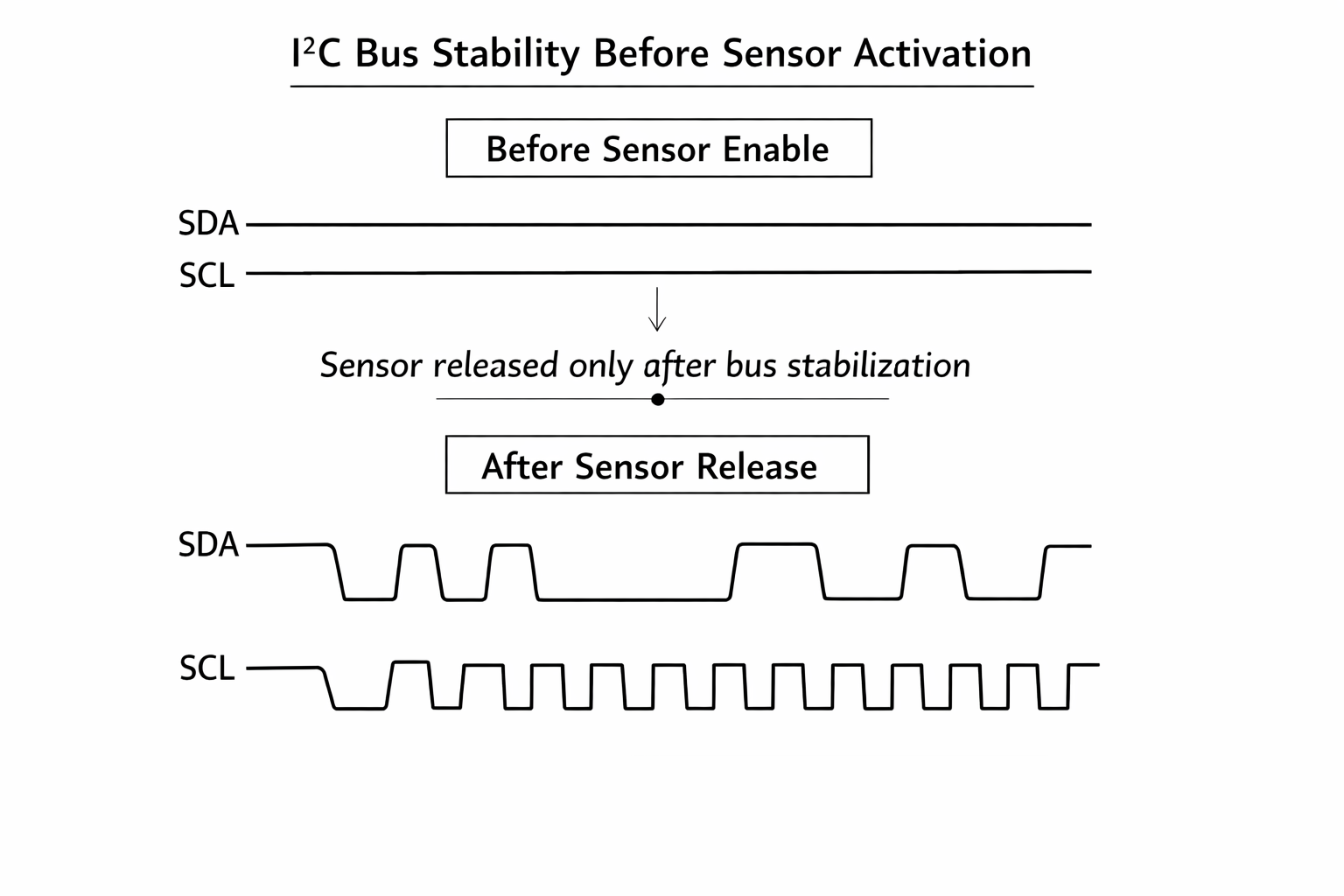

Bus Stability Before Sensor Activation

Communication buses such as I²C or SPI must be stable before sensors begin transmitting.

If sensors wake up before pull-ups stabilise or before the MCU configures the bus, the result can be:

- Bus contention

- Clock stretching deadlocks

- Stuck SDA lines

To prevent this, we enforce a simple rule:

Sensors remain in shutdown until the bus is known to be stable.

Only after the MCU configures the bus do we release sensors from shutdown.

This guarantees that the first communication transaction occurs under controlled conditions.

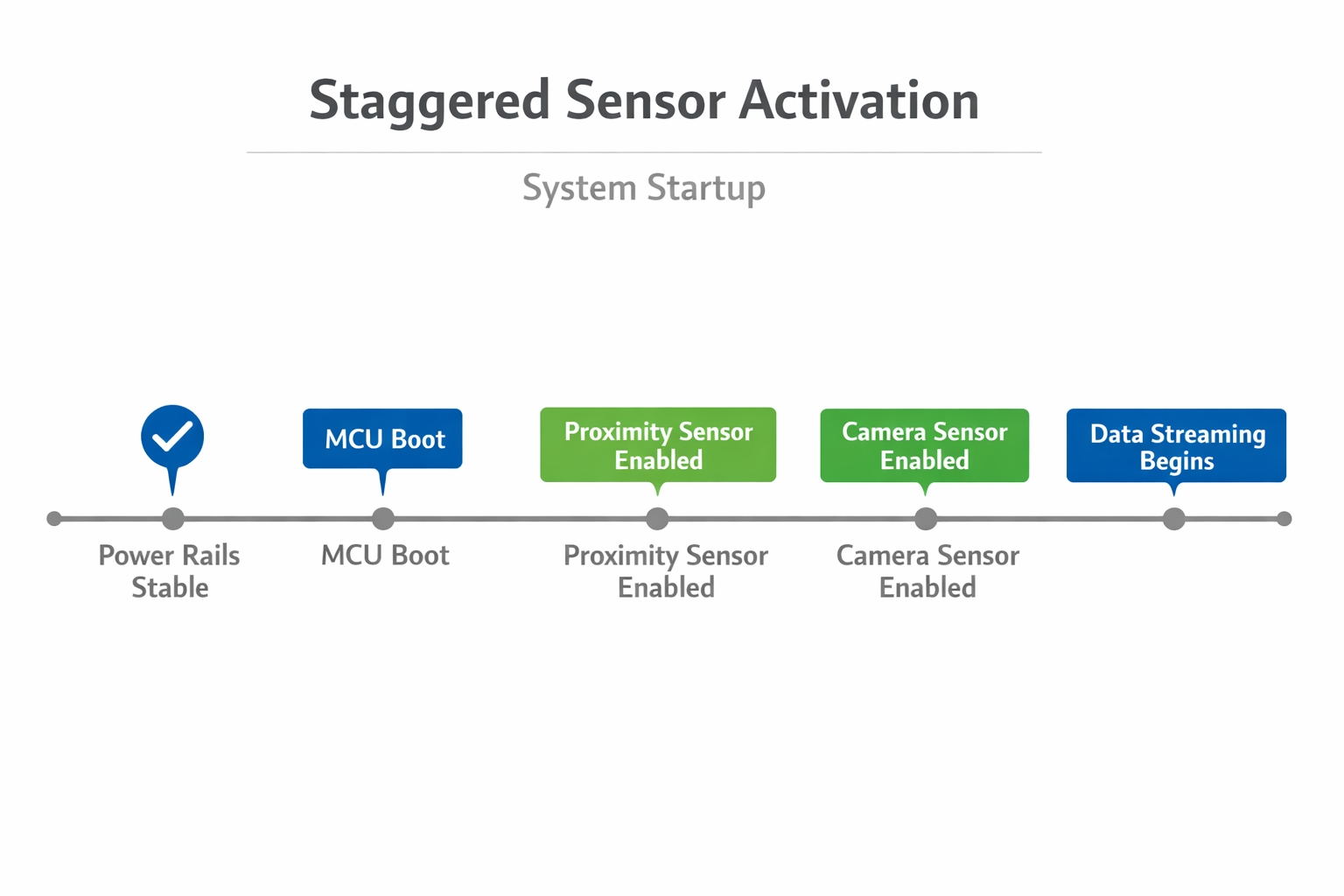

Preventing Startup Contention Between Sensors

Multiple sensors sharing a bus can compete during startup.

If two devices attempt to communicate simultaneously before the MCU establishes control, unpredictable states can occur.

We prevent this by staggering sensor activation.

Instead of powering all sensors together, we release them sequentially.

For example:

- Proximity sensor activated

- Communication verified

- Image sensor released

- Data streaming enabled

This approach ensures that only one new subsystem becomes active at a time.

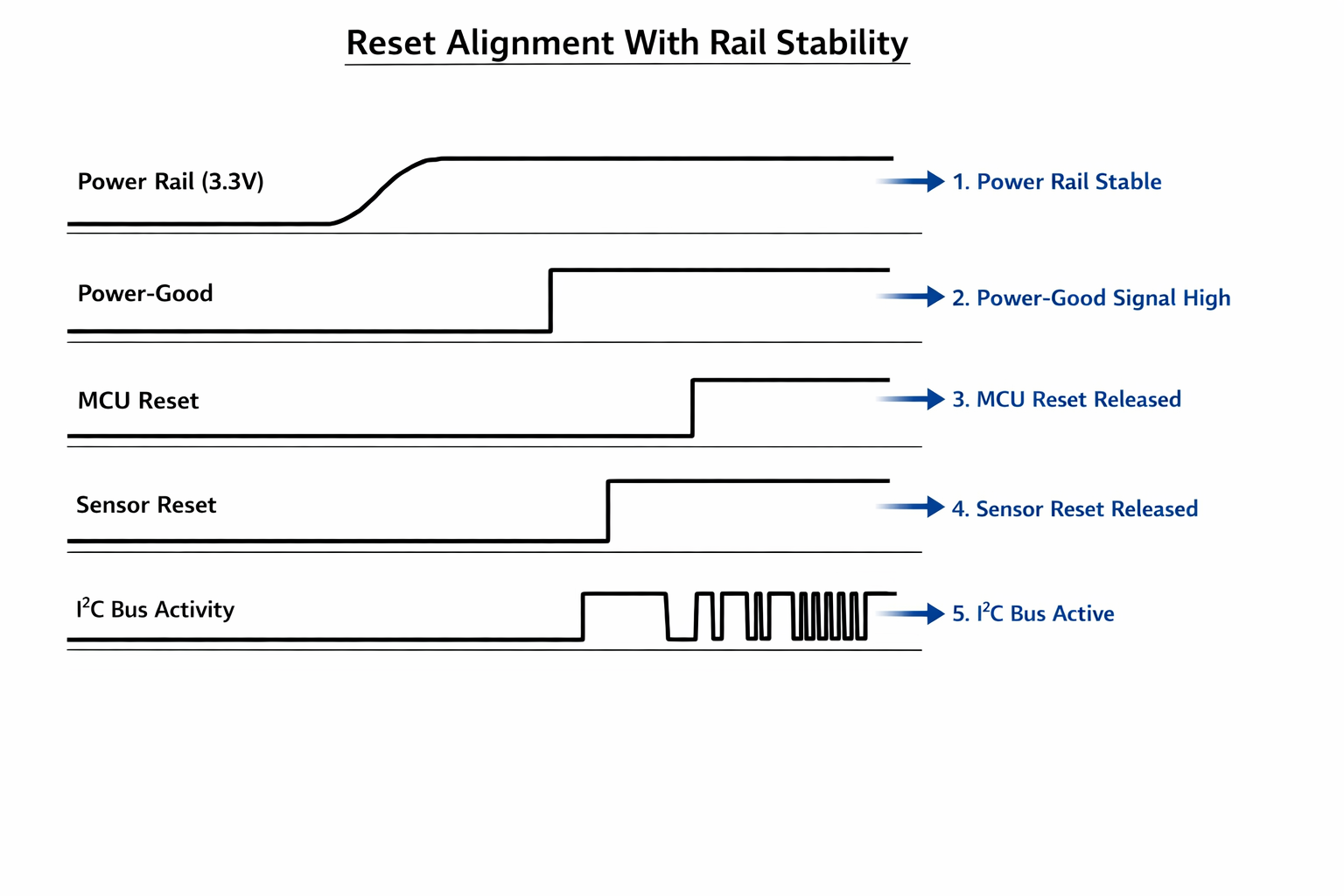

Reset Alignment Across Subsystems

Power-up order is closely related to reset behaviour.

If reset signals are not aligned with rail stability, sensors may initialise incorrectly.

To address this, we design a reset architecture carefully.

For example:

- MCU reset controlled by the supervisor IC

- Sensor resets gated by power-good signals

- Communication interfaces held in idle state

This ensures that sensors always begin operation from a known state.

What Happens When Sensors Are Powered Incorrectly

Improper startup ordering can produce several symptoms.

Some of the most common include:

- Sensors not responding on the bus

- Data streams containing invalid frames

- Interrupt lines stuck active

- Unexpected current draw

These issues can be extremely difficult to reproduce because they depend on timing.

A system might work perfectly in the lab but fail intermittently in the field.

By enforcing power-up order in hardware, we eliminate those timing uncertainties.

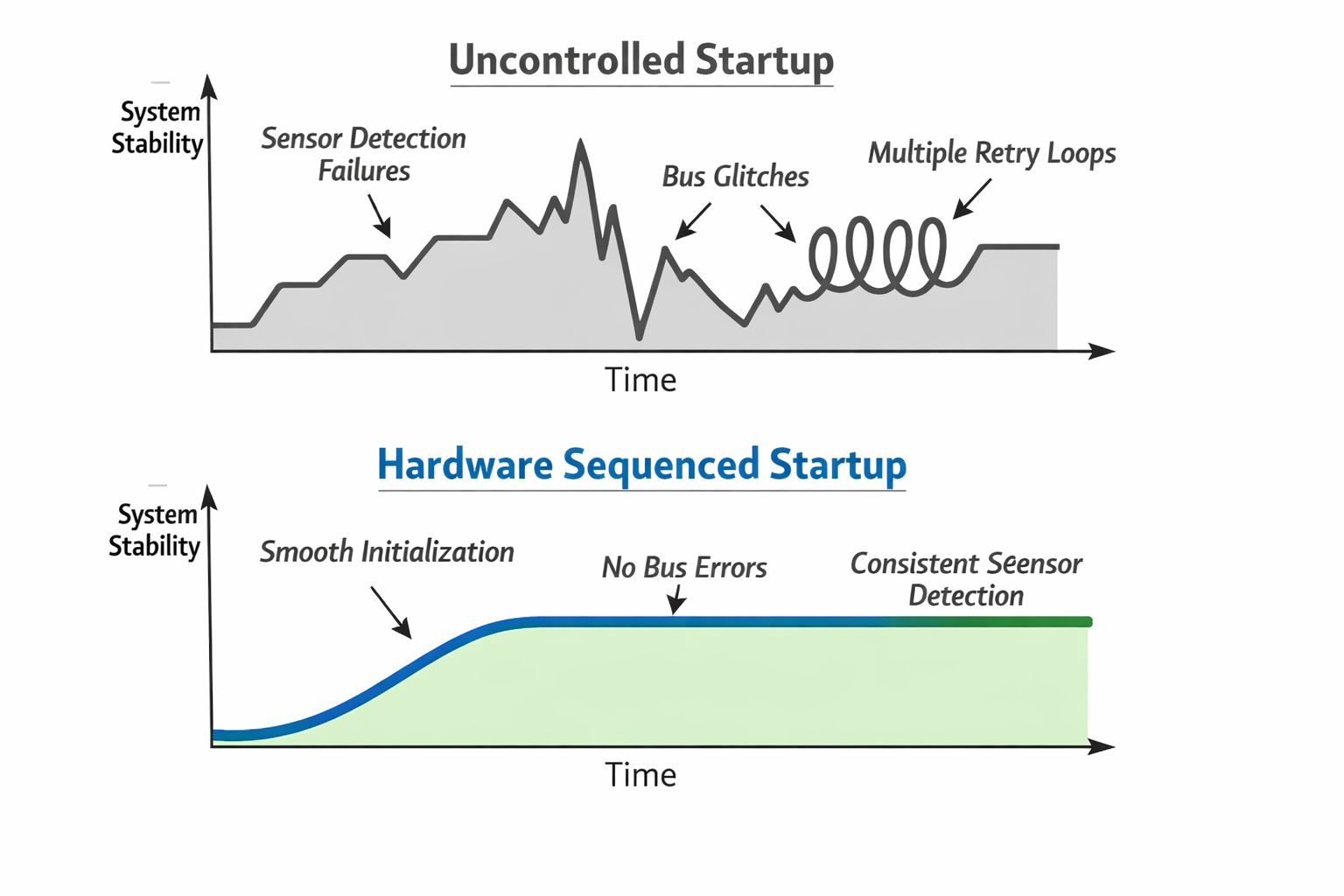

Measuring the Impact of Deterministic Sensor Startup

After implementing hardware-enforced sensor sequencing, we observed several measurable improvements.

Improved Boot Reliability

Sensor detection during startup became completely repeatable.

Cold-start initialisation errors were eliminated.

Faster Stable Initialisation

Because sensors started in the correct state every time, firmware no longer needed extended retry loops.

System initialisation became faster and more predictable.

Reduced Bus Lockups

I²C bus errors during startup were significantly reduced because sensors only joined the bus after stabilisation.

Lower Startup Current Spikes

Staggered activation prevented multiple sensors from drawing peak current simultaneously.

More Predictable Debugging

Startup timing could be measured and validated with an oscilloscope, making failures easier to diagnose.

Designing the Power-Up Timeline

Instead of treating startup as a single event, we define it as a sequence of stages.

A typical sensor system startup timeline may look like this:

- Input power becomes stable

- Core MCU rail powers up

- IO rail stabilises

- Communication buses configured

- Sensor power domains enabled

- Sensors released from shutdown

- Data interfaces activated

Each stage has clear dependencies.

Nothing proceeds until the previous step is verified.

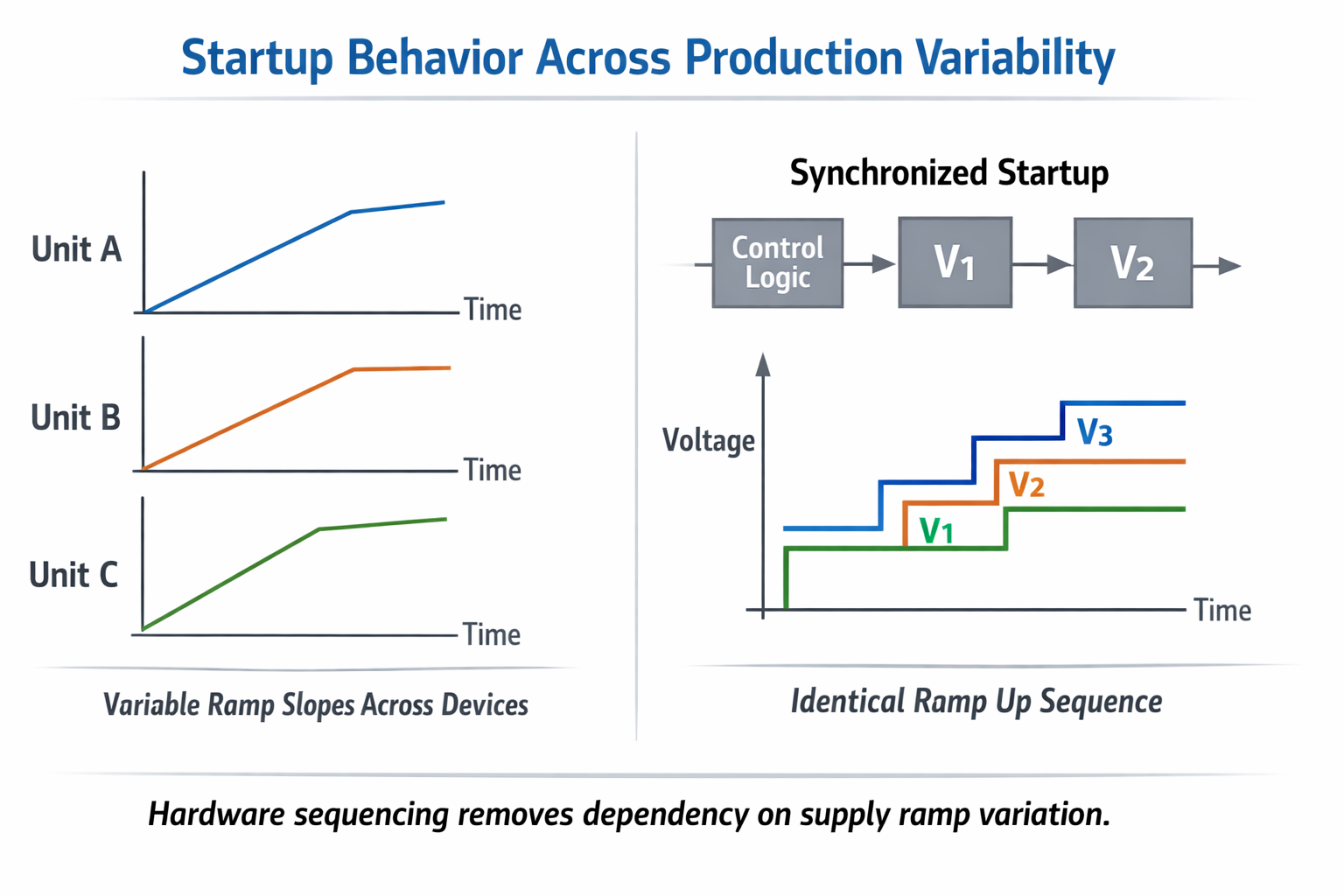

Why Hardware Sequencing Matters in Production

A prototype may appear stable even without strict sequencing.

But production environments introduce variations that expose hidden weaknesses.

These variations include:

- Different power supplies

- Temperature fluctuations

- Component tolerance differences

- Aging regulators

Hardware-enforced sequencing ensures that these variations do not affect startup behaviour.

The system behaves identically across all units.

Designing for the Worst Case

The true test of a startup architecture is not ideal conditions.

It is the worst case:

- Low battery voltage

- Cold temperature

- Slow regulator ramp

- Brownout recovery

If sensors still initialise correctly under these conditions, the system is robust.

This is why we validate sequencing with real measurements rather than assumptions.

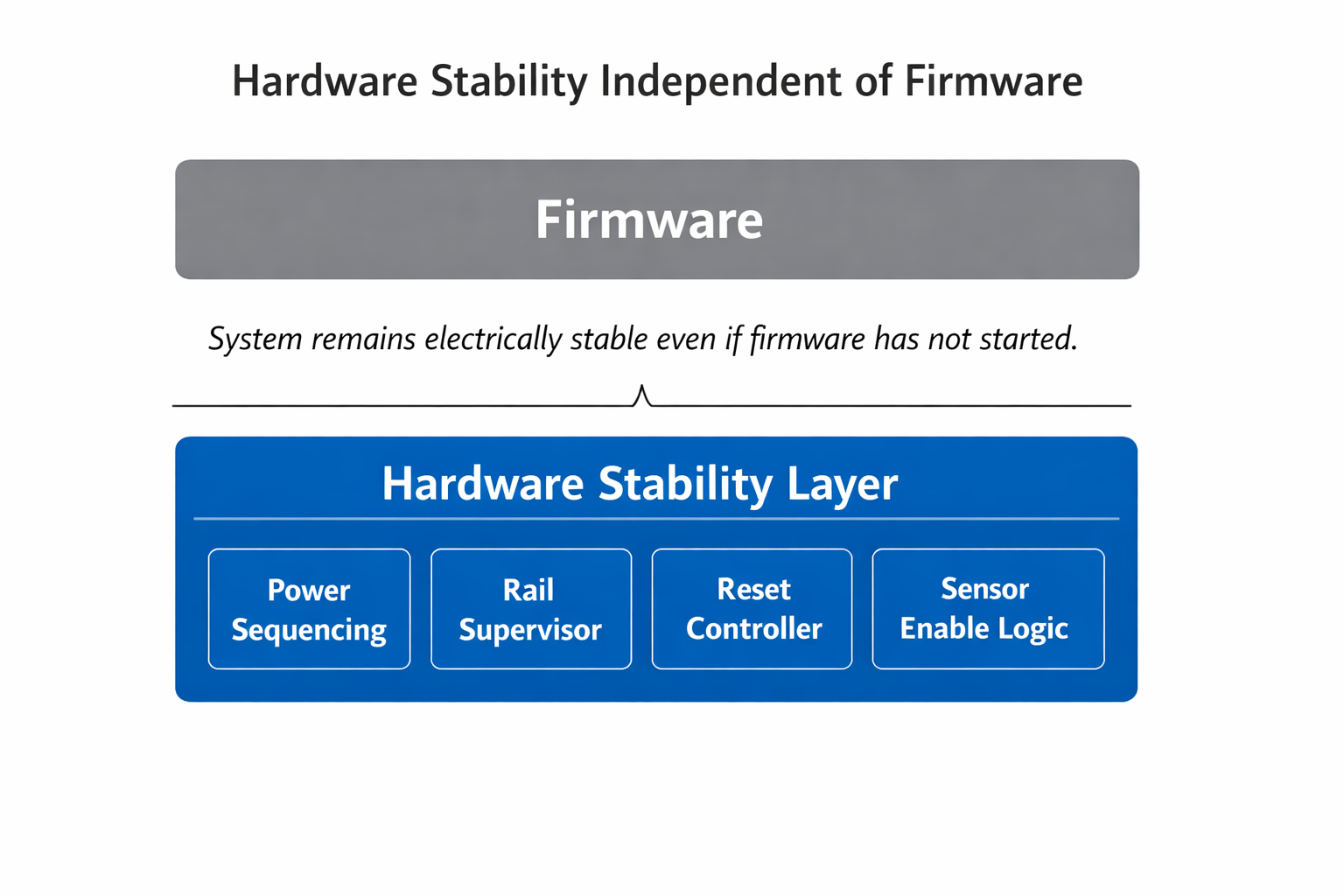

Hardware Before Firmware

One of the key principles we follow is simple:

The hardware must behave correctly even if firmware is not running.

If the MCU crashes during boot, the system should remain electrically safe.

Sensors should not enter undefined states.

Buses should remain stable.

Firmware should enhance functionality — not compensate for hardware uncertainty.

The Core Design Principle

Sensor systems are not just collections of devices.

They are coordinated electrical ecosystems.

Each subsystem depends on others behaving predictably.

By enforcing sensor startup order in hardware, we transform boot behaviour from a race condition into a controlled sequence.

The result is a system that starts correctly every time — not just most of the time.

And in embedded products, that difference defines the line between a prototype and a reliable product.