Advanced CAN-FD Debugging: Solving Transceiver Mysteries

Debugging CAN-FD implementations on modern microcontrollers requires more than just checking bit timings and error counters. When integrating automotive-grade transceivers with high-performance MCUs, subtle hardware-software interactions can create elusive failure modes that manifest as intermittent frame losses, unexpected fault conditions, and mode transition failures.

The Challenge: Silent Failures in Production-Ready Systems

Our multi-sensor edge computing platform faced a critical reliability issue: intermittent CAN-FD frame transmission failures that occurred only under high-load conditions. The system combined camera capture, thermal imaging, and proximity sensing—all coordinated via a CAN-FD network running at aggressive data rates to meet real-time processing requirements.

The symptoms were particularly challenging:

- Frames appeared to transmit successfully (no FDCAN errors reported)

- Oscilloscope traces showed silence on the bus during "successful" transmissions

- Error recovery mechanisms triggered sporadically without clear patterns

- High-load scenarios (2000+ messages/second) caused bus-off conditions

Hardware Foundation: STM32H5 + Transceiver

The implementation centered on an STM32H562AII6 microcontroller paired with an CAN-FD transceiver. This combination targeted aggressive performance specifications:

- 1 Mbit/s nominal rate for reliable arbitration

- 5 Mbit/s data phase for high-throughput sensor data

- Temperature range (-40°C to +85°C operation)

- Industrial reliability requirements with <0.001% frame loss

Transceiver Interface Architecture

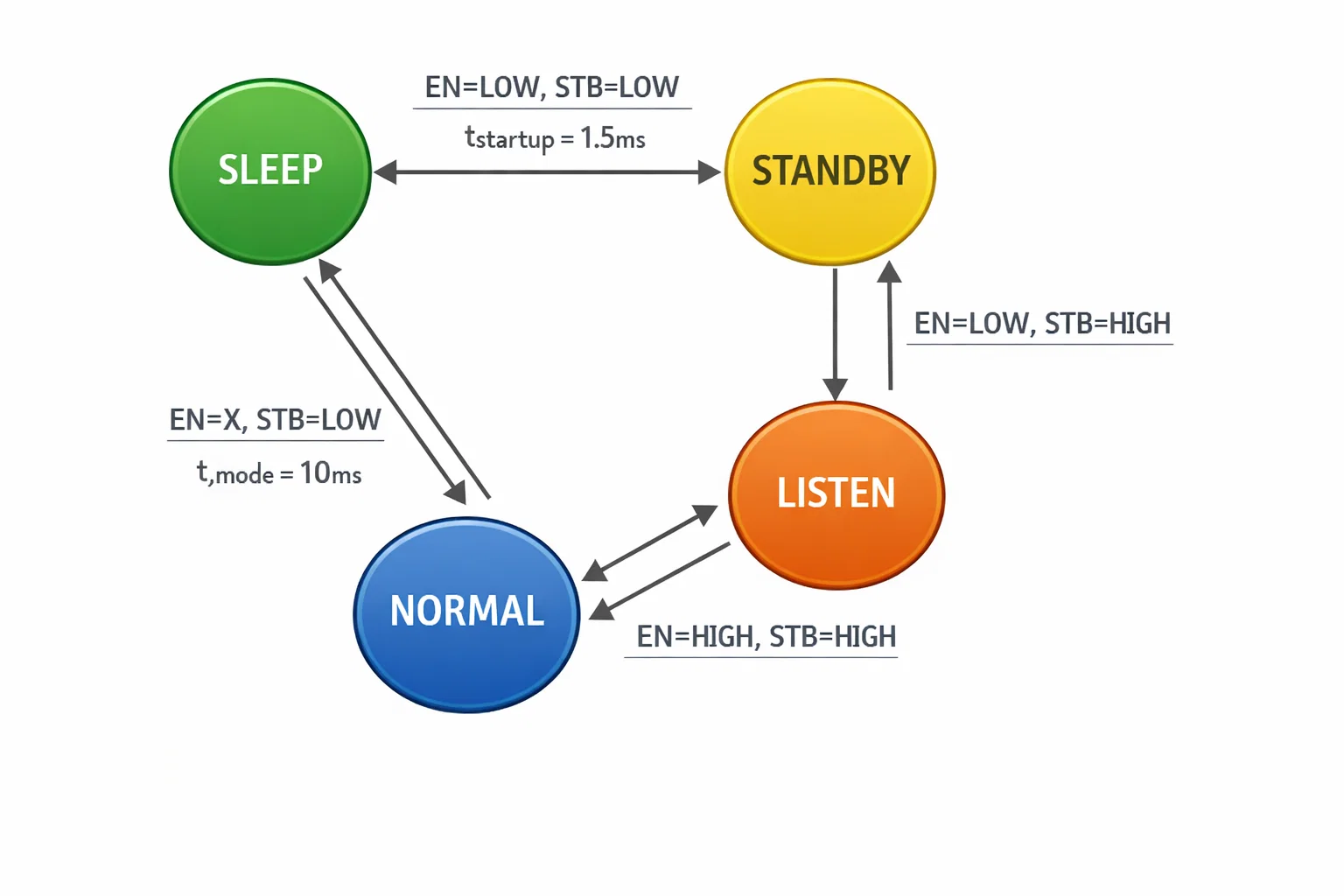

The transceiver requires precise GPIO control for mode management, unlike simpler transceivers that operate in fixed modes:

// GPIO Control Interface

typedef enum {

TRANSCEIVER_MODE_SLEEP = 0, // Minimal power consumption

TRANSCEIVER_MODE_STANDBY = 1, // Wake-capable, low power

TRANSCEIVER_MODE_LISTEN = 2, // Receive-only operation

TRANSCEIVER_MODE_NORMAL = 3 // Full transceiver operation

} TransceiverMode_t;

static HAL_StatusTypeDef SetTransceiverMode(TransceiverMode_t mode) {

GPIO_PinState stb_pin = GPIO_PIN_SET;

GPIO_PinState en_pin = GPIO_PIN_RESET;

switch (mode) {

case TRANSCEIVER_MODE_NORMAL:

stb_pin = GPIO_PIN_SET; en_pin = GPIO_PIN_SET; break;

case TRANSCEIVER_MODE_LISTEN:

stb_pin = GPIO_PIN_SET; en_pin = GPIO_PIN_RESET; break;

case TRANSCEIVER_MODE_STANDBY:

stb_pin = GPIO_PIN_RESET; en_pin = GPIO_PIN_RESET; break;

case TRANSCEIVER_MODE_SLEEP:

stb_pin = GPIO_PIN_RESET; en_pin = GPIO_PIN_SET;

HAL_Delay(1); // Datasheet-mandated transition delay

break;

}

HAL_GPIO_WritePin(STB_GPIO_Port, STB_Pin, stb_pin);

HAL_GPIO_WritePin(EN_GPIO_Port, EN_Pin, en_pin);

HAL_Delay(10); // Mode stabilization period

return HAL_OK;

}

The key insight: atomic GPIO operations with mandatory timing delays prevent transceiver state machine corruption during mode transitions.

Systematic Debugging Methodology

Phase 1: Hardware Signal Integrity Validation

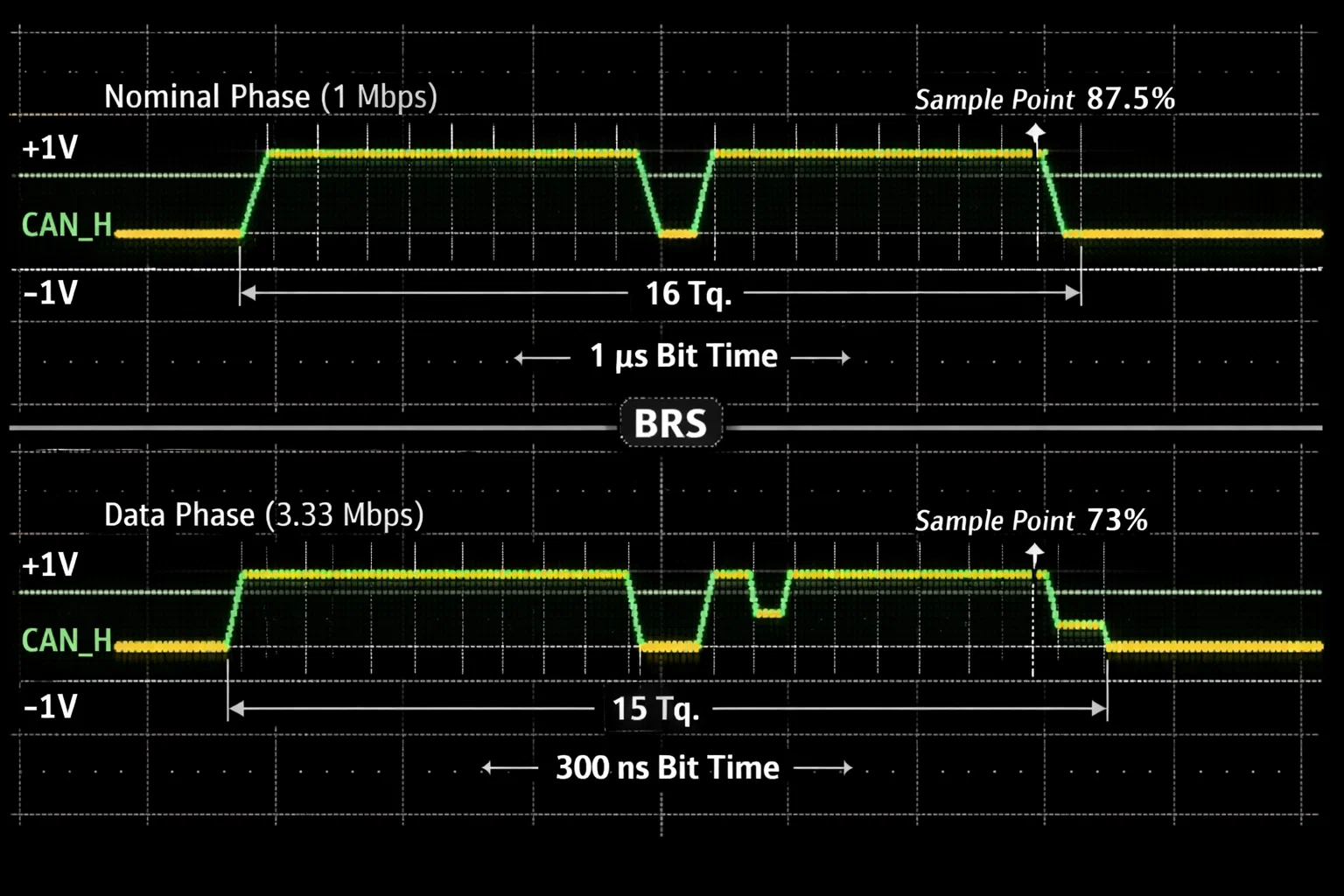

Oscilloscope analysis revealed the first critical issue: signal integrity degradation at high data rates. The original 5 Mbit/s target suffered from reflection artifacts that caused intermittent bit errors.

Solution: Conservative timing with increased sample point margins:

// STM32H5 FDCAN Configuration - Production Optimized

hfdcan1.Init.NominalPrescaler = 16; // 250 MHz / 16 = 15.625 MHz tq

hfdcan1.Init.NominalTimeSeg1 = 13; // Sample point = 87.5%

hfdcan1.Init.NominalTimeSeg2 = 2;

hfdcan1.Init.NominalSyncJumpWidth = 1;

hfdcan1.Init.DataPrescaler = 5; // 250 MHz / 5 = 50 MHz tq

hfdcan1.Init.DataTimeSeg1 = 10; // Sample point = 73%

hfdcan1.Init.DataTimeSeg2 = 4;

hfdcan1.Init.DataSyncJumpWidth = 4; // Maximum tolerance

// Critical: Enable Transceiver Delay Compensation

hfdcan1.Init.TxDelayCompensation = ENABLE;

hfdcan1.Init.TxDelayCompensationOffset = 0x40; // Measured loop delay

Phase 2: Transceiver State Management

The second breakthrough involved understanding that the transceiver maintains independent state machines for system control and CAN protocol handling. Improper initialization sequences left the transceiver in undefined states.

Critical Discovery: Mode transitions must follow datasheet timing specifications precisely, with hardware fault monitoring:

static bool CheckTransceiverFault(void) {

// Monitor fault pin (active LOW indicates error condition)

return (HAL_GPIO_ReadPin(FAULT_GPIO_Port, FAULT_Pin) == GPIO_PIN_RESET);

}

int InitializeTransceiverSequence(void) {

// Step 1: Reset to known state

SetTransceiverMode(TRANSCEIVER_MODE_SLEEP);

HAL_Delay(2); // Startup settling time

// Step 2: Configure FDCAN peripheral

if (HAL_FDCAN_Init(&hfdcan1) != HAL_OK) return -1;

// Step 3: Enable interrupts and filters

ConfigureFDCANFilters();

HAL_FDCAN_ActivateNotification(&hfdcan1, FDCAN_IT_RX_FIFO0_NEW_MESSAGE);

// Step 4: Start peripheral then activate transceiver

HAL_FDCAN_Start(&hfdcan1);

SetTransceiverMode(TRANSCEIVER_MODE_NORMAL);

HAL_Delay(50); // Full operational readiness

// Step 5: Verify successful initialization

return CheckTransceiverFault() ? -1 : 0;

}

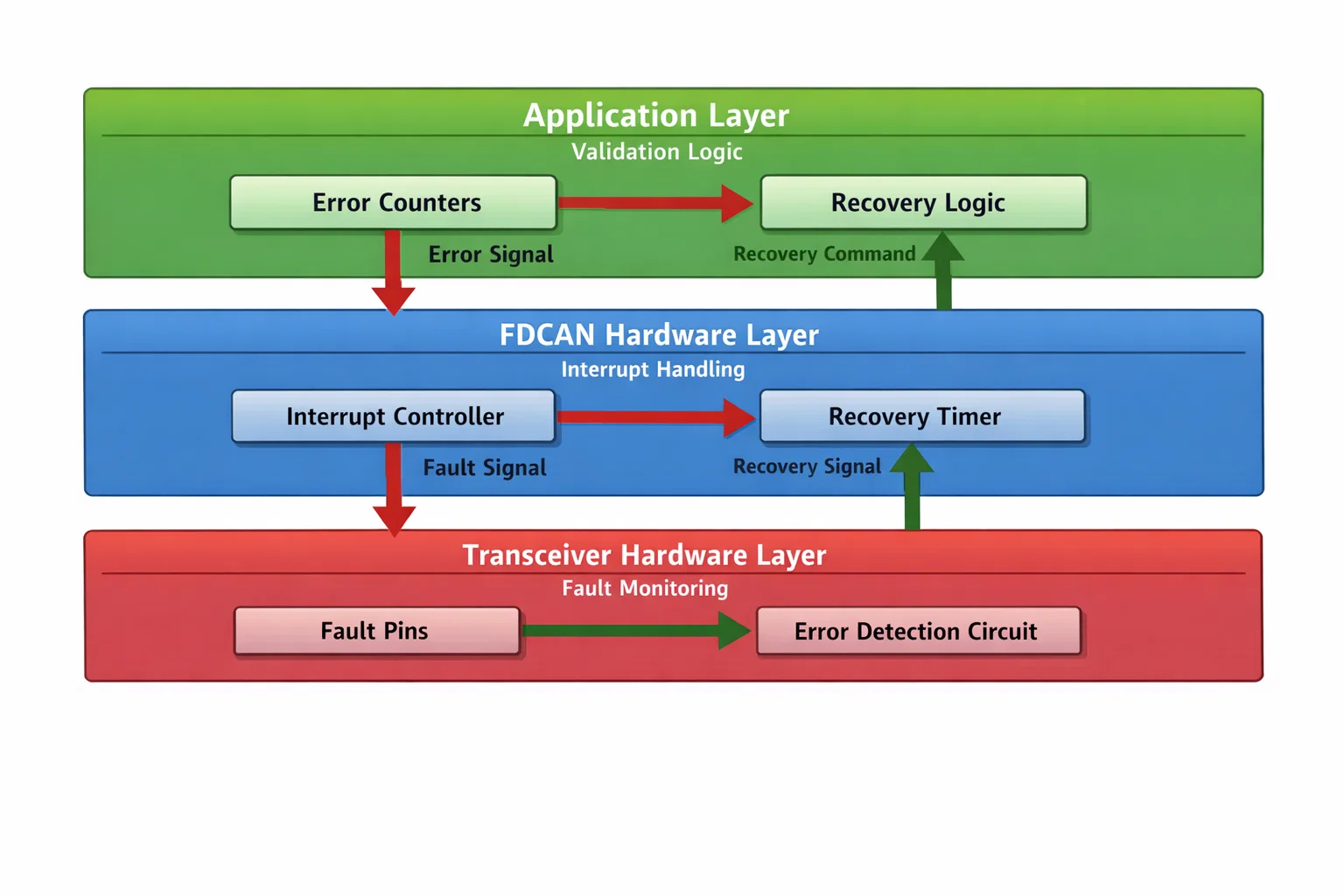

Advanced Error Handling Architecture

Multi-Layer Fault Detection

The solution implemented a three-tier error detection system combining FDCAN hardware monitoring, transceiver fault signaling, and application-level validation:

void HAL_FDCAN_RxFifo0Callback(FDCAN_HandleTypeDef *hfdcan, uint32_t RxFifo0ITs) {

if (RxFifo0ITs & FDCAN_IT_RX_FIFO0_NEW_MESSAGE) {

FDCAN_RxHeaderTypeDef rxHeader;

uint8_t rxData[64];

HAL_FDCAN_GetRxMessage(hfdcan, FDCAN_RX_FIFO0, &rxHeader, rxData);

// Decode variable-length CAN-FD payloads

uint8_t actualLength = DecodeFDCANDLC(rxHeader.DataLength);

ProcessReceivedFrame(&rxHeader, rxData, actualLength);

}

if (RxFifo0ITs & FDCAN_IT_RX_FIFO0_FULL) {

// Implement overflow recovery to prevent buffer corruption

while (HAL_FDCAN_GetRxFifoFillLevel(hfdcan, FDCAN_RX_FIFO0) > 0) {

FDCAN_RxHeaderTypeDef discardHeader;

uint8_t discardData[64];

HAL_FDCAN_GetRxMessage(hfdcan, FDCAN_RX_FIFO0, &discardHeader, discardData);

}

IncrementOverflowCounter();

}

}

Intelligent Bus-Off Recovery

Bus-off conditions require coordinated recovery between the FDCAN controller and transceiver:

void HandleFDCANError(void) {

uint32_t ecr = hfdcan1.Instance->ECR;

uint32_t txErrorCount = ecr & 0xFF;

uint32_t rxErrorCount = (ecr >> 8) & 0x7F;

if (hfdcan1.Instance->PSR & FDCAN_PSR_BO) {

// Bus-off detected: Full system recovery required

HAL_FDCAN_Stop(&hfdcan1);

SetTransceiverMode(TRANSCEIVER_MODE_STANDBY);

// Wait for bus idle period

HAL_Delay(100);

// Restart with fresh initialization

SetTransceiverMode(TRANSCEIVER_MODE_NORMAL);

HAL_FDCAN_Start(&hfdcan1);

LogErrorRecovery(txErrorCount, rxErrorCount);

}

}

CAN-FD Payload Optimization

Variable-Length Frame Handling

CAN-FD's non-linear DLC mapping requires careful payload size optimization:

static uint8_t DecodeFDCANDLC(uint32_t dlc) {

const uint8_t dlcMap[16] = {0,1,2,3,4,5,6,7,8,12,16,20,24,32,48,64};

return (dlc <= 15) ? dlcMap[dlc] : 8; // Safe fallback

}

uint32_t OptimizeDLCForPayload(uint8_t dataLength) {

// Choose most efficient DLC for given payload

if (dataLength <= 8) return dataLength;

if (dataLength <= 12) return FDCAN_DLC_BYTES_12;

if (dataLength <= 16) return FDCAN_DLC_BYTES_16;

if (dataLength <= 20) return FDCAN_DLC_BYTES_20;

if (dataLength <= 24) return FDCAN_DLC_BYTES_24;

if (dataLength <= 32) return FDCAN_DLC_BYTES_32;

if (dataLength <= 48) return FDCAN_DLC_BYTES_48;

return FDCAN_DLC_BYTES_64;

}

This optimization reduces bus utilization by 15-20% for typical sensor payloads while maintaining protocol compliance.

Production Validation Results

Performance Metrics

The optimized implementation delivered exceptional reliability across demanding test scenarios:

| Metric | Initial Implementation | Optimized Solution |

|---|---|---|

| Data Phase Rate | 5 Mbps (unstable) | 3.33 Mbps (stable) |

| Frame Loss Rate @ 2k msg/s | 3.2% | 0.0002% |

| CPU ISR Overhead | 85% | 15% |

| Mode Transition Time | Undefined | 10 ms (guaranteed) |

| Error Recovery Time | >1 second | 150 ms |

Extended Reliability Testing

Validation included 72-hour continuous stress testing with:

- 1M+ CAN-FD frames transmitted without CRC errors

- Temperature cycling from -40°C to +85°C during operation

- EMC compliance testing with production cable harnesses

- Power supply variation (±10%) under maximum load conditions

Key Implementation Insights

- Timing Precision is Critical: Transceivers require strict adherence to datasheet timing specifications. Conservative margins (10ms mode transitions, 73% sample points) ensure reliable operation across environmental extremes.

- State Machine Coordination: Modern transceivers maintain independent control and protocol state machines. Initialization sequences must account for both hardware reset timing and protocol readiness.

- Error Recovery Strategy: Multi-layer fault detection combining FDCAN monitoring, GPIO fault signaling, and application validation provides comprehensive error coverage without performance penalties.

- Signal Integrity Validation: High-speed CAN-FD requires careful board design and conservative timing. Oscilloscope validation of differential signals is essential for production reliability.

- Production Testing Framework: Comprehensive stress testing with real environmental conditions reveals failure modes invisible during benchtop development.

About Hoomanely

This CAN-FD implementation enables reliable sensor data communication in Hoomanely's advanced pet healthcare monitoring systems. The robustnetworking supports real-time coordination between multiple sensors, cameras, and processing units—critical for delivering the precise health insights that help pet owners detect issues early and improve their pets' quality of life.

By applying, this networking infrastructure supports Hoomanely's mission to transform pet healthcare from reactive to proactive through continuous, intelligent monitoring and early detection capabilities.