Clock Tree Jitter & High-Speed I/O: How Internal Clock Jitter Impacts DCMI Capture Reliability at the Physical Limit

In the world of embedded vision systems, every nanosecond matters. When pushing the boundaries of high-speed camera interfaces, one often-overlooked factor can make the difference between crystal-clear captures and corrupted frames: internal clock jitter. This isn't just theoretical noise—it's a real-world challenge that directly impacts the reliability of DCMI (Digital Camera Interface) systems operating at their physical limits.

The Hidden Enemy: Understanding Clock Jitter in Real Systems

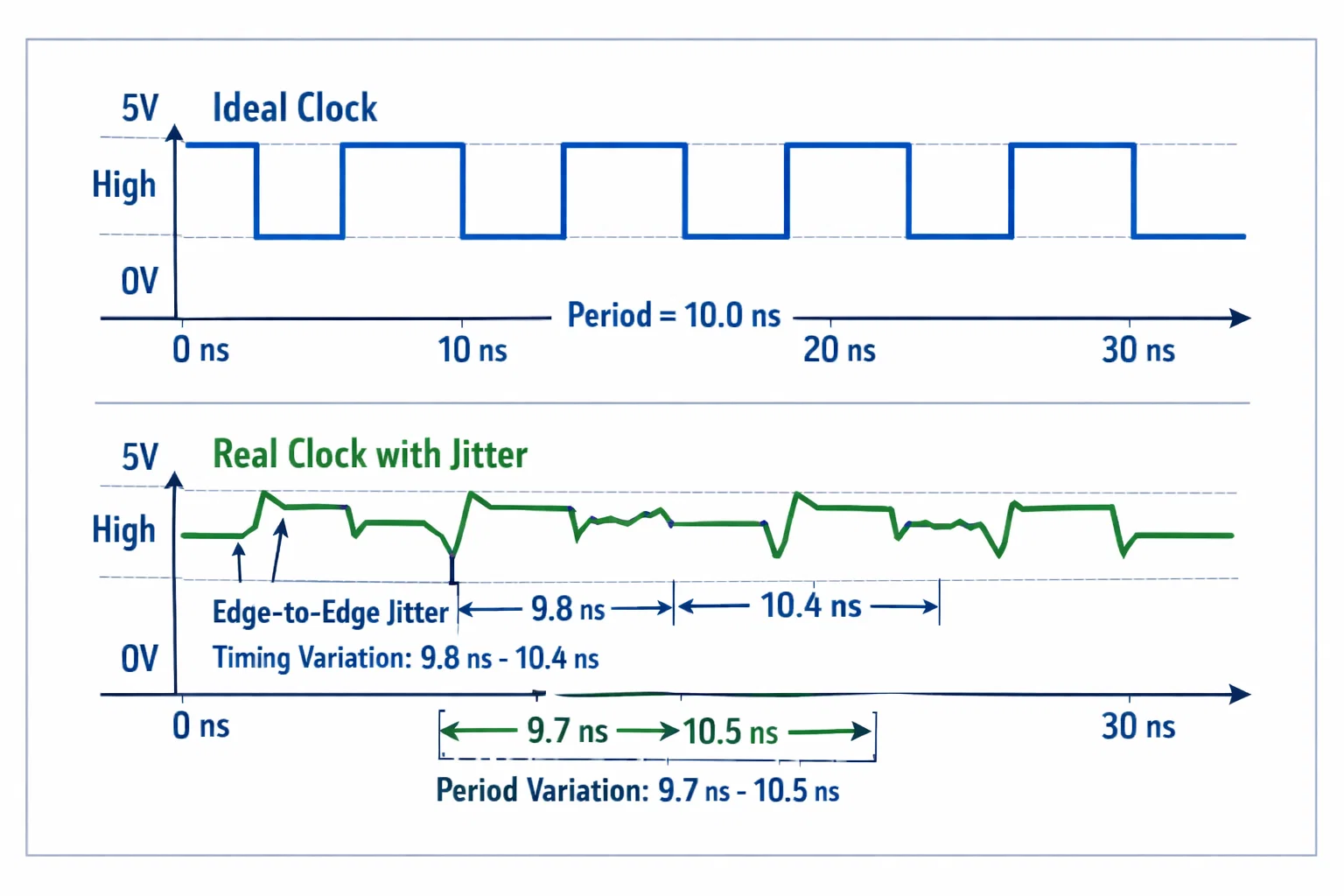

Clock jitter represents the deviation of timing events from their ideal positions. In a perfect world, every clock edge would arrive precisely when expected. Reality tells a different story. Modern microcontrollers, despite their sophistication, introduce measurable timing variations that cascade through the entire system.

Key Takeaway: Clock jitter isn't just a specification number—it's a dynamic phenomenon that varies with temperature, supply voltage, electromagnetic interference, and system load.

Why DCMI Systems Are Particularly Vulnerable

Digital camera interfaces operate under extremely tight timing constraints. Consider a typical high-resolution camera sensor outputting pixel data at rates exceeding 100 MHz. At these frequencies, even picosecond-level timing variations can accumulate into significant errors.

The Cascade Effect

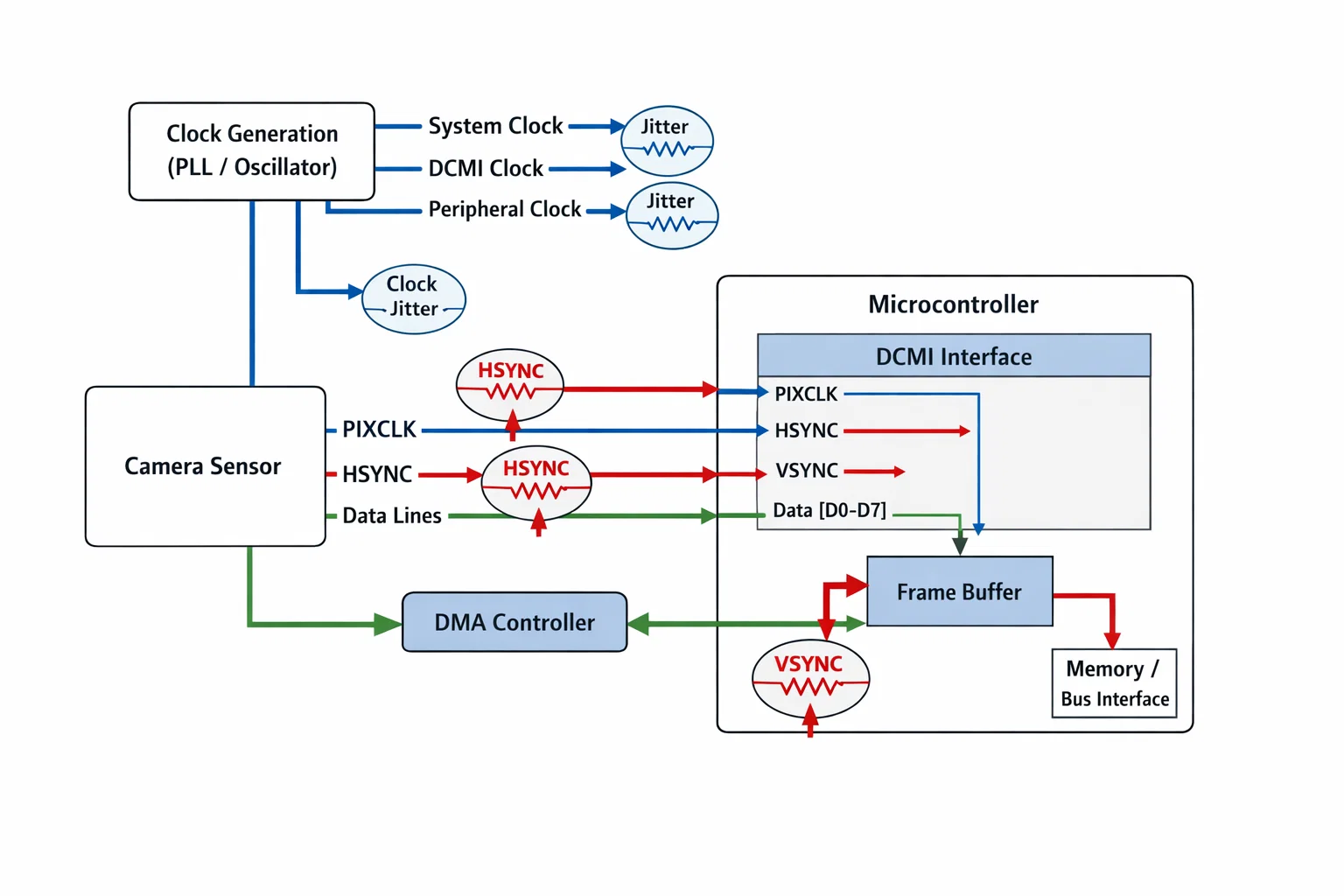

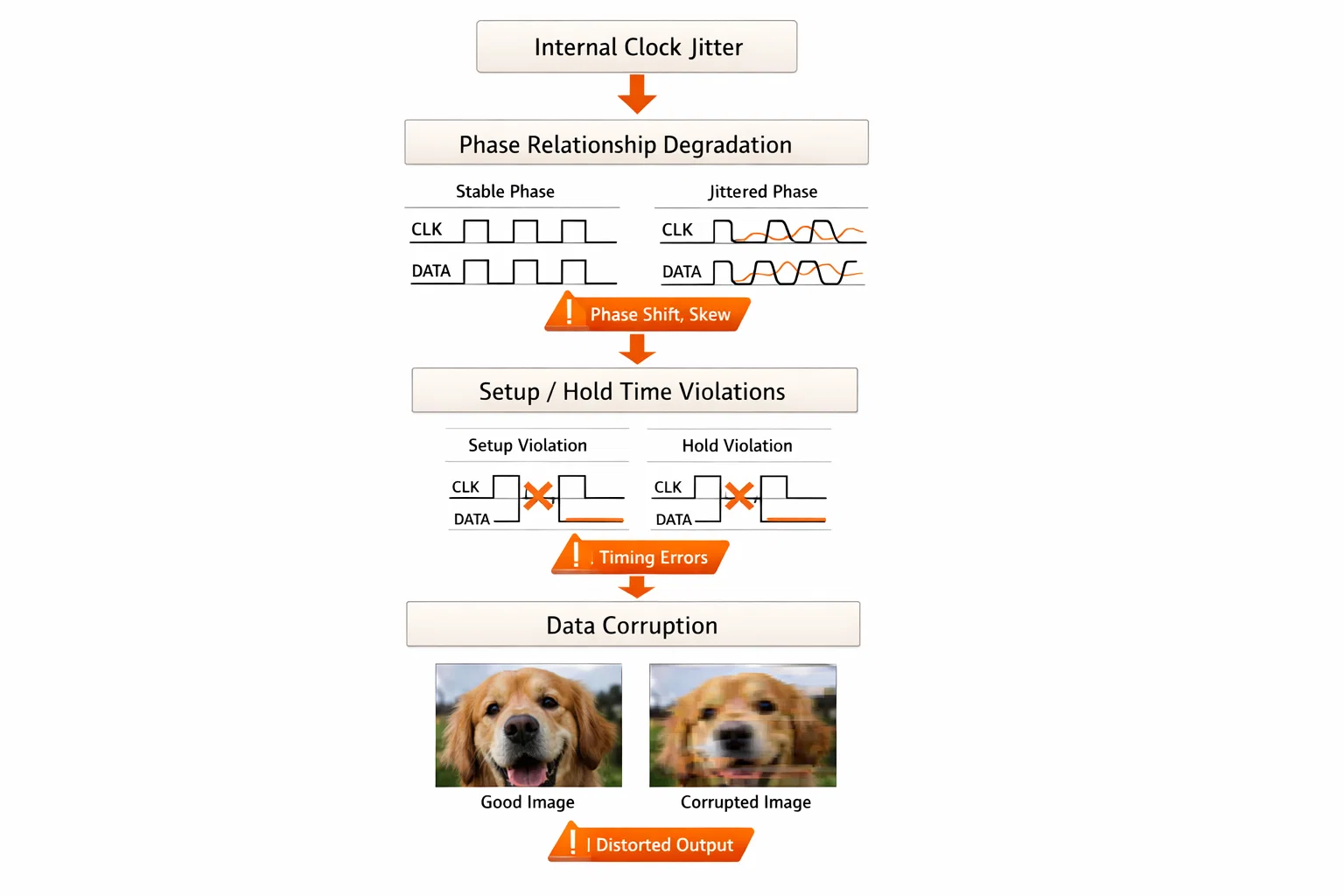

When internal clock jitter affects the pixel clock (PIXCLK) generation, it creates a domino effect:

- Phase Relationship Degradation: The delicate timing relationship between PIXCLK, HSYNC, and VSYNC signals becomes unstable

- Setup/Hold Time Violations: Critical timing windows for data sampling shrink unpredictably

- Data Corruption: Pixels arrive at unexpected moments, leading to misaligned or lost data

Real-World Impact: Where Theory Meets Practice

In high-performance embedded vision applications, the symptoms of clock jitter manifest as:

- Intermittent Frame Corruption: Random horizontal lines or color artifacts appearing sporadically

- Synchronization Loss: Camera interface occasionally losing sync, requiring system resets

- Reduced Maximum Frame Rates: Systems that should theoretically support higher speeds failing in practice

- Environmental Sensitivity: Performance degradation under specific temperature or EMI conditions

The DCMI Configuration Dilemma

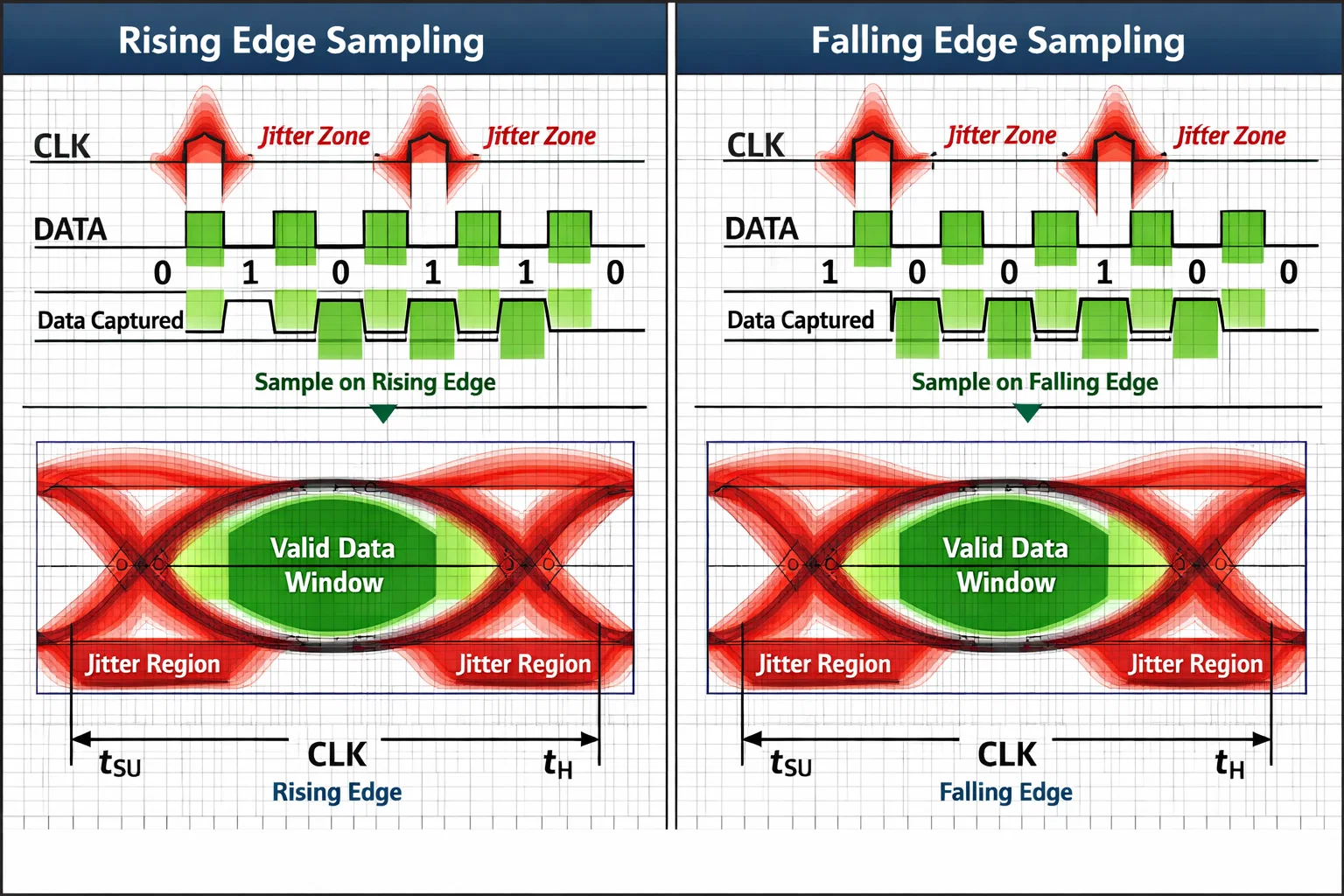

Modern embedded systems offer flexibility in clock edge selection, but this choice carries significant implications. The decision between DCMI_PCKPOLARITY_FALLING and DCMI_PCKPOLARITY_RISING isn't arbitrary—it determines which phase of the pixel clock captures incoming data.

When internal jitter shifts the effective sampling point, one polarity might provide better noise margins than the other. This explains why switching clock polarities sometimes "magically" fixes intermittent capture issues.

The Clock Tree Architecture Challenge

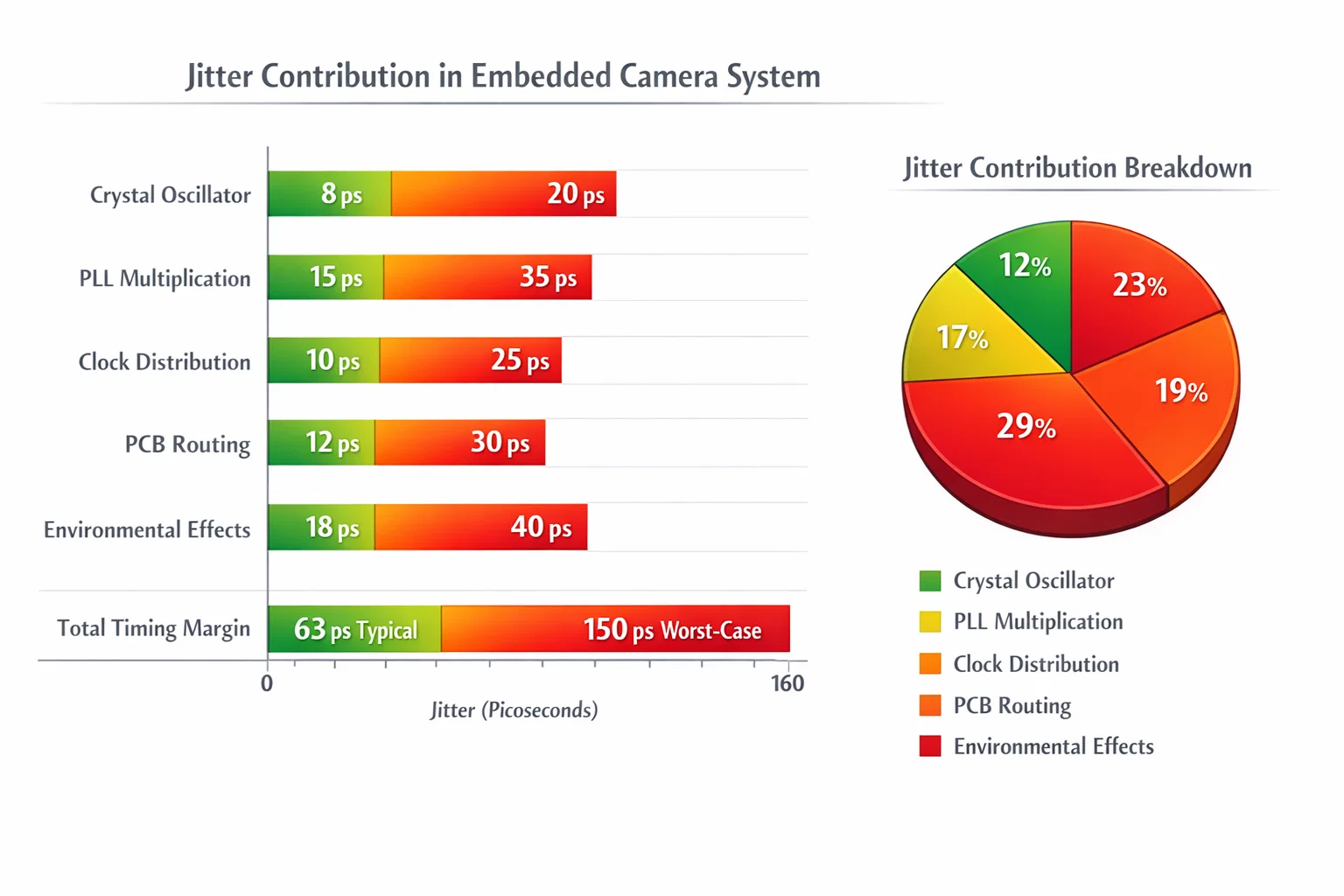

Understanding the path from crystal oscillator to pixel clock reveals multiple jitter introduction points:

Primary Sources of Internal Jitter

PLL Multiplication Chains: Each phase-locked loop in the clock generation path adds its own jitter contribution. High multiplication ratios, while achieving desired frequencies, amplify existing noise.

Clock Distribution Networks: On-chip routing introduces skew and jitter through RC delays and crosstalk. High-frequency signals are particularly susceptible to supply noise coupling.

Dynamic Loading Effects: As peripheral activity changes, the effective capacitive load on clock networks varies, introducing timing variations.

Mitigation Strategies: Engineering Around Reality

Hardware-Level Approaches

Dedicated Clock Domains: Isolating timing-critical interfaces on separate clock trees reduces cross-coupling effects. This strategy proves particularly effective for camera interfaces sharing die space with high-activity peripherals.

Supply Filtering: Clean power delivery to clock generation circuits significantly reduces jitter. Dedicated LDO regulators for PLL supplies often justify their cost through improved timing stability.

PCB Layout Optimization: Careful routing of high-speed signals, proper ground planes, and strategic component placement minimize external jitter sources.

Firmware Optimization Techniques

Adaptive Polarity Selection: Implementing runtime detection of optimal clock polarity based on capture quality metrics provides robustness across manufacturing variations.

Synchronization Verification: Continuous monitoring of HSYNC/VSYNC timing relationships enables early detection of jitter-induced problems.

Buffer Management: Strategic frame buffer allocation and DMA configuration can provide additional tolerance for timing variations.

The Measurement Challenge

Quantifying clock jitter in embedded systems requires sophisticated techniques:

Time Interval Analysis: Using high-resolution oscilloscopes to measure period-to-period jitter provides insight into short-term variations.

Eye Diagram Analysis: Overlaying many clock cycles reveals the timing uncertainty envelope affecting data capture windows.

Statistical Characterization: Long-term jitter measurements help predict reliability under various operating conditions.

Hoomanely's Vision

At Hoomanely, we're revolutionizing pet healthcare through precision monitoring technology. Our approach combines Edge AI with multi-sensor fusion to generate clinical-grade intelligence at home. This technical foundation directly benefits from understanding timing-critical system design.

When developing wearable devices that continuously monitor pet health metrics, every sensor interface must operate reliably under diverse conditions. The camera systems capturing behavioral patterns, the biosensors monitoring vital signs, and the wireless communications maintaining connectivity—all depend on robust timing design that accounts for real-world clock jitter effects.

Our commitment to precision-driven healthcare extends to the fundamental engineering choices that ensure data integrity. By mastering these timing challenges, we enable the breakthrough combination of Edge AI and sensor fusion that transforms raw health data into personalized insights for pet care.

Beyond the Specifications

The true measure of timing robustness isn't found in datasheet specifications—it emerges from understanding the interaction between all system elements. Temperature cycling, supply variations, electromagnetic environments, and manufacturing tolerances all influence real-world clock jitter performance.

Critical Insight: Systems operating at their timing limits require design margins that account for worst-case jitter accumulation, not just typical values.

Key Takeaways

- Clock jitter is cumulative: Multiple sources throughout the clock generation and distribution chain add up to create system-level timing uncertainty.

- Environmental sensitivity matters: Temperature, supply voltage, and electromagnetic interference all influence jitter characteristics in ways that pure simulation cannot predict.

- Interface timing is system timing: DCMI reliability depends on the entire clock tree architecture, not just the immediate pixel clock generation.

- Measurement enables optimization: Comprehensive jitter characterization reveals the specific mechanisms limiting system performance.

- Design for resilience: Robust timing design incorporates adaptive strategies and monitoring capabilities to maintain performance across operating conditions.

This exploration into clock tree jitter and high-speed I/O timing draws from real-world experiences with demanding embedded vision applications. The challenges discussed here represent genuine engineering problems that require both theoretical understanding and practical innovation to solve effectively.

As we continue pushing the boundaries of what's possible in embedded systems—whether for pet healthcare monitoring or other precision applications—mastering these timing fundamentals becomes increasingly critical. The intersection of hardware limits and software intelligence demands nothing less than excellence in every design decision.