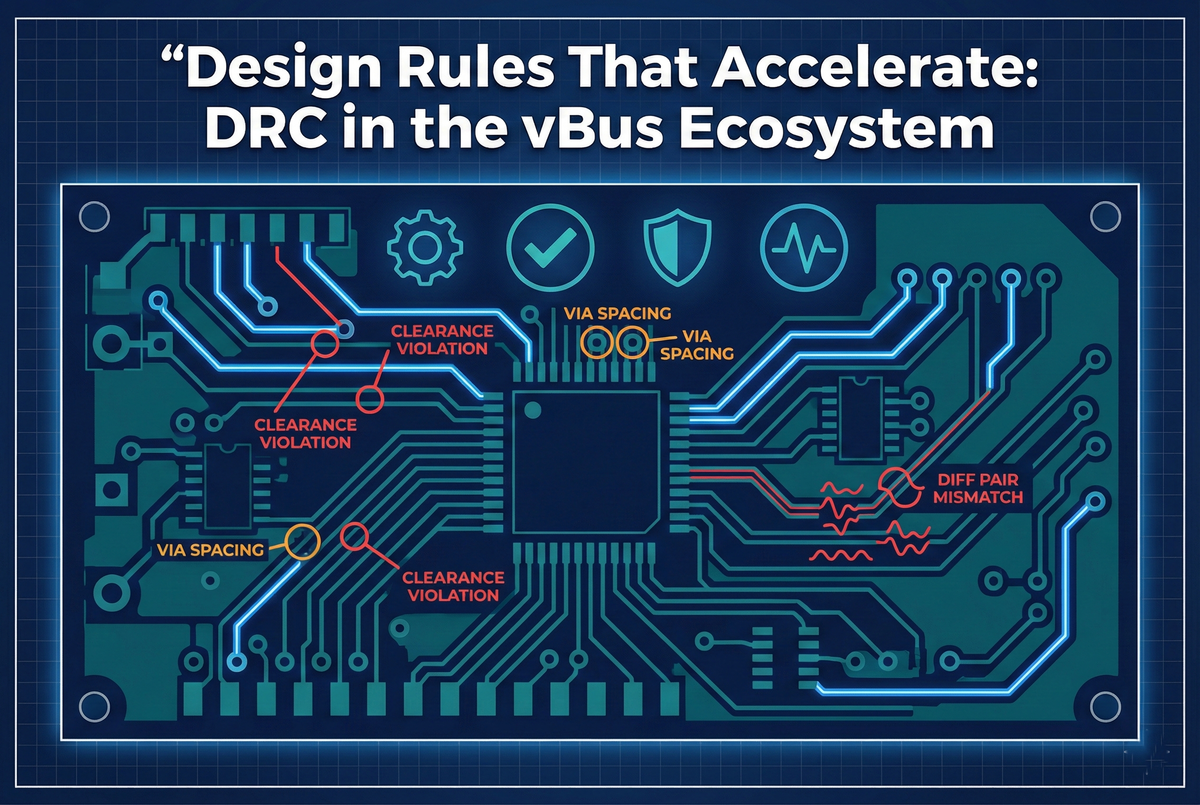

Design Rules That Work: PCB DRC at Scale in the vBus Ecosystem

Introduction: Rules That Enable, Not Obstruct

At Hoomanely, Design Rule Checking (DRC) isn't a bureaucratic hurdle—it's an intelligent validation layer that catches real manufacturing issues while keeping design velocity high. As our vBus product portfolio has grown, we've refined our DRC philosophy: rules must catch genuine problems that would cause manufacturing failures, while never blocking progress on valid design decisions.

Our approach targets the sweet spot: comprehensive rules tuned to real-world manufacturing capabilities, applied consistently across every vBus module we design.

Manufacturing-Driven Rules

Our DRC rules directly reflect PCB manufacturer capabilities. Every rule ties to a specific constraint:

Trace Width and Spacing:

- Minimum trace width: 6 mil (0.15mm) - 20% above manufacturer's 5 mil minimum for process margin

- Minimum clearance: 6 mil standard, 20 mil for high-voltage signals

- Power traces: Width calculated per IPC-2221 based on current requirements

Via Specifications:

- Minimum drill: 8 mil (0.2mm) finished hole

- Minimum annular ring: 4 mil from drill edge to pad edge

- Via-in-pad: Flagged for review (requires special manufacturing)

High-Speed Signal Rules:

- Differential pairs: Matched width ±10%, length matching within 5 mil

- Return path verification: Continuous ground plane under signals

- Via stubs: Flagged when exceeding 20 mil on high-speed signals

Component Placement:

- Component to board edge: 50 mil minimum

- Component to component: 20 mil minimum

- Component to mounting hole: 100 mil clearance

These aren't theoretical—they're validated against actual manufacturing process data from our fabrication partners.

vBus-Specific Design Rules

Connector Pin-Out Validation

DRC scripts automatically validate against vBus standards:

- Power pins positioned correctly

- Signal pins match specification

- Multiple pins allocated for high-current rails

- Ground pins maintain 1:1 ratio with power pins

Signal Naming Convention

Automated checks ensure compliance:

- Power nets:

[VOLTAGE]_[TYPE]_[DOMAIN]format - Signal nets:

[INTERFACE]_[SIGNAL]_[DESTINATION]format - Control signals:

[FUNCTION]_[TYPE]_[TARGET]format

Non-compliant names flagged with correction suggestions.

Module-Specific Rules

CPU SoM Requirements:

- DDR routing length matching: ±5 mil for address/command, ±25 mil for data

- Decoupling capacitors within 200 mil of power pins

- Thermal vias: Minimum 30 under processors

Power SoM Requirements:

- High current trace widths validated against actual requirements

- Thermal vias under switching regulators and MOSFETs

- Component placement per IC datasheet guidelines

Peripheral SoM Requirements:

- Guard rings around high-impedance analog signals

- I2C pull-up resistor verification

- Interrupt traces routed to interrupt-capable pins

Communication SoM Requirements:

- RF traces: 50Ω controlled impedance

- Antenna keep-out zones enforced

- EMI shielding and grounding verified

DRC Execution Framework

Real-Time Checking

Modern EDA tools provide instant feedback—violations appear as designer works:

- Prevents error accumulation

- Corrections made during routing, not after

- Visual indicators show violations immediately

Batch Validation

Full comprehensive check before review or manufacturing:

- Detailed report with violation count per category

- Specific locations (layer, coordinates) for each issue

- Severity classification (error, warning, info)

- Resolution suggestions included

Design Review Integration

Pre-Review Requirement: Zero DRC errors mandatory before scheduling review. Reviewers focus on design intent, not basic violations.

Warning Review: Non-critical warnings reviewed in meeting—justified design decisions vs. actual concerns.

Rule Tuning and Evolution

Manufacturing Feedback Loop

First-pass yield tracked per design—high yield validates rules, lower yield triggers investigation:

- Were violations missed?

- Do rules need adjustment?

- New failure modes discovered?

When manufacturing issues occur, DRC updated to catch similar problems in future designs.

Technology Updates

As manufacturing capabilities improve, rules evolve:

- Tighter tolerances enable higher density designs

- New processes require rule updates

- Enhanced capabilities reflected in relaxed constraints where appropriate

Designer Feedback

Engineers provide valuable input:

- False positives identified and rules adjusted

- Missing checks added based on field experience

- Rule clarity improved based on usage patterns

Production Timeline Benefits

Eliminating PCB Re-spins

Every re-spin costs 5-9 weeks plus financial impact. Our >95% first-pass success rate means most designs work correctly on first manufactured revision—DRC catches issues before fabrication.

Accelerating Design Reviews

Pre-cleared DRC enables reviewers to focus on:

- Architectural decisions

- Signal integrity optimization

- Component selection strategy

- Thermal management approaches

Result: Design reviews complete 30-40% faster when mechanical violations are pre-cleared.

Manufacturing Confidence

Consistent DRC adherence builds fabricator trust:

- Designs known to meet capabilities

- Reduced pre-production questions

- Faster quotes and turnaround

- Occasional priority scheduling access

Parallel Development

vBus modularity allows simultaneous module development. DRC standardization ensures integration success:

- Connector pinouts validated

- Signal naming consistent

- No mechanical interference

Teams design CPU, Power, and Peripheral SoMs in parallel, confident DRC-validated designs integrate on first assembly.

Key Performance Metrics

First-Pass Success Rate: >95% of designs manufactured successfully on first revision

Design Review Efficiency: 30-40% faster completion when DRC pre-validates

Rule Hit Analysis: Tracks which rules trigger most—identifies training needs and rule tuning opportunities

Time to Clean DRC: Monitored per designer and project—indicates design complexity and training effectiveness

Conclusion: Quality at Speed

PCB DRC at scale is intelligent automation that catches real issues while maintaining design velocity. Our approach—manufacturing-driven rules, continuous validation, feedback-driven tuning—ensures DRC serves as a quality multiplier.

The results: >95% first-pass success, faster design reviews, eliminated manufacturing delays, and confident parallel development across our vBus portfolio. DRC isn't overhead—it's infrastructure enabling us to design better products faster.

As our ecosystem grows, our DRC framework evolves with it. New modules adopt established rules immediately. Manufacturing feedback refines rules continuously. Automation handles mechanical verification, freeing engineers for innovation.

This is engineering discipline at scale—systematic quality assurance that compounds across every design. When design rules are tuned correctly, they don't slow you down—they propel you forward with confidence.