Manufacturing Intelligence: Pick-and-Place Standardization in the vBus Ecosystem

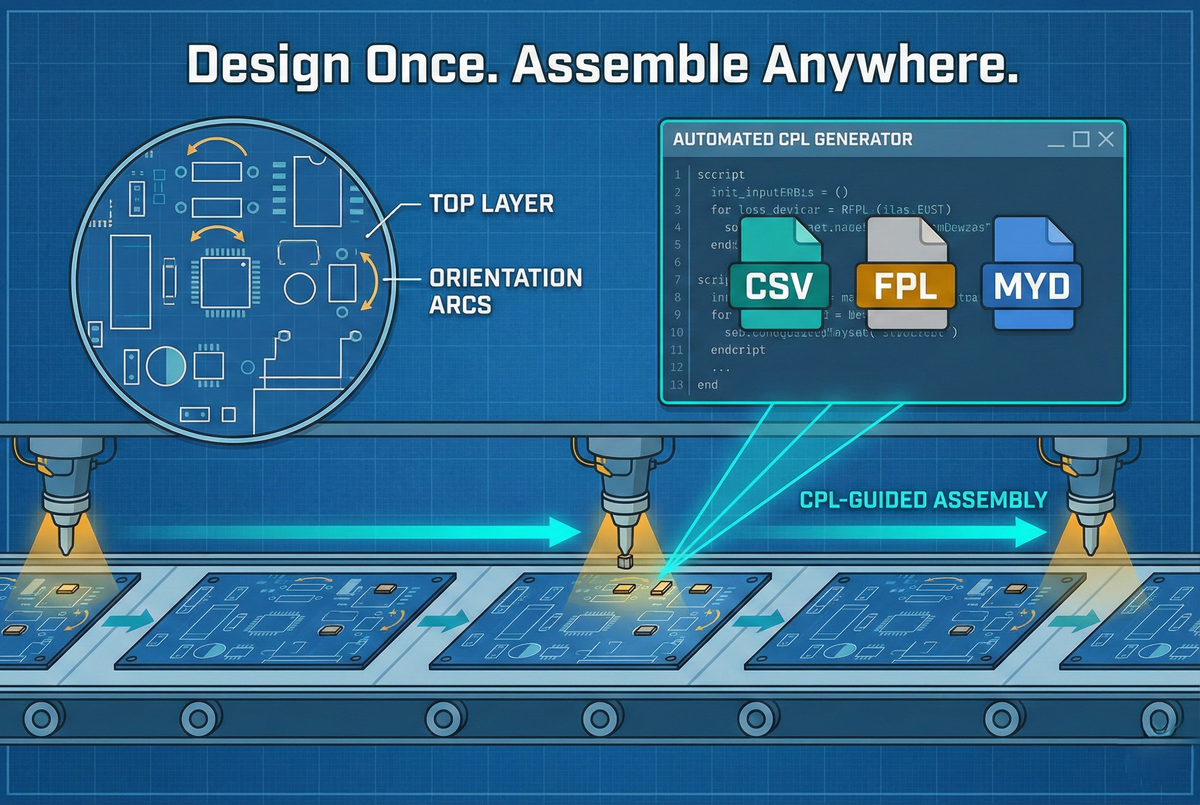

Every PCB design carries an invisible but critical responsibility: to communicate clearly with the machines that will bring it to life. The CPL is that language. It tells automated assembly lines exactly what to place and where, converting engineering intent into manufacturing reality. When this translation is crisp, production is uneventful. When it isn’t, engineers and operators spend hours debugging coordinates instead of building products.

As hardware systems become modular and manufacturing ecosystems global, the cost of inconsistent or ambiguous CPL data compounds quickly. The solution isn’t better guesswork at the factory—it’s disciplined, predictable CPL generation at the design stage. Treating placement data as a structured engineering asset rather than an export button dramatically improves reliability, portability, and throughput for every module produced.

The Vendor Portability Problem

Every Manufacturer is Different

Pick-and-place machines speak different dialects:

- Machine formats: Some use CSV, others proprietary formats (Mydata MYD, Fuji FPL)

- Origin conventions: Board origin might be bottom-left, center, or top-left depending on machine

- Rotation standards: 0° reference differs between vendors—component orientation relative to what?

- Unit systems: Metric (mm) vs. imperial (mils/inches)

- Column ordering: X/Y/Rotation/Designator order varies

Traditional approach: Generate CPL from CAD tool, send to manufacturer, wait for feedback on format issues, manually correct, re-send. Repeat for each new vendor.

Problem: This iteration wastes 2-5 days per design per vendor and introduces transcription errors.

The Multi-Vendor Reality

We work with multiple contract manufacturers:

- Prototyping vendor: Quick-turn, low volume, high flexibility

- Production vendor: High volume, optimized processes, cost-efficient

- Regional vendors: Local assembly for specific markets

- Backup vendors: Business continuity and capacity overflow

Each has different equipment. Each requires correctly formatted CPL. Managing this complexity manually doesn't scale.

The vBus CPL Standard: One Source, Many Targets

Master CPL Format

We've defined a canonical CPL format—our internal standard from which all vendor-specific formats derive:

Column Structure:

Designator, Mid X, Mid Y, Layer, Rotation, Comment

U1, 25.40, 15.24, Top, 0, STM32H743ZIT6_LQFP144

C1, 22.86, 12.70, Top, 90, 0.1uF_0402

R1, 27.94, 17.78, Bottom, 180, 10K_0603

Standards Enforced:

- Origin: Board geometric center (0, 0)

- Units: Millimeters with 2 decimal places

- Rotation: 0° = component marking upward (top layer) or downward (bottom layer), increases counter-clockwise

- Layer: Explicit Top/Bottom designation

- Designator: Matches schematic reference designator exactly

- Comment: Human-readable component description for verification

Benefits:

- Vendor-neutral (no assumptions about target machine)

- Human-readable (engineers can visually verify correctness)

- Consistent rotation reference (eliminates most common placement error)

- Complete information (includes all data any vendor might need)

Automated Format Conversion

From master CPL, we generate vendor-specific formats automatically:

Conversion Script: Python-based translator reads master CPL, applies transformation rules:

Origin Translation:

Convert from center origin to bottom-left origin

new_x = master_x + (board_width / 2)

new_y = master_y + (board_height / 2)

Rotation Conversion:

Convert from counter-clockwise to clockwise if needed

if vendor_uses_clockwise:

new_rotation = 360 - master_rotation

Column Reordering: Map master columns to vendor template:

vendor_format = {

'RefDes': master['Designator'],

'PosX': master['Mid X'],

'PosY': master['Mid Y'],

'Side': 1 if master['Layer'] == 'Top' else 2,

'Rot': master['Rotation'],

'Type': master['Comment']

}

Output: Vendor-ready CPL in their preferred format, generated in seconds.

Vendor Profile Library

We maintain profiles for each manufacturer:

Profile Contents:

- Machine format specification (CSV structure, delimiters)

- Origin convention (center, bottom-left, top-left)

- Rotation standard (CW vs. CCW, 0° reference)

- Unit preference (mm vs. mils)

- Special requirements (fiducial handling, panel notation)

Usage: Designer selects vendor profile, script generates appropriate CPL automatically. New vendor? Add profile once, use forever.

Component Library Integration

Placement Data at the Source

CPL accuracy starts in component libraries:

Footprint Metadata: Each footprint includes standardized placement data:

- Pick point: X/Y offset from footprint origin to component center (where nozzle grabs)

- Component height: Z-dimension for nozzle clearance

- Rotation offset: Correction factor if component's 0° differs from standard orientation

Example—LQFP144 Package:

Pick point: (0, 0) — center of package

Height: 1.6mm — package thickness plus clearance

Rotation offset: 0° — pin 1 at standard position

Example—0402 Capacitor:

Pick point: (0, 0) — component center

Height: 0.5mm — standard 0402 thickness

Rotation offset: 0° — no preferred orientation (symmetric)

Benefit: When component is placed in PCB layout, placement data flows automatically to CPL—no manual entry, no transcription errors.

Component Orientation Standards

Polarized Components: Consistent orientation rules enforced:

- ICs: Pin 1 toward top-left of board

- Electrolytic capacitors: Positive terminal toward top or right

- Diodes/LEDs: Cathode marking toward right or bottom

- Connectors: Pin 1 toward board edge

Non-Polarized Components: Standard orientation where practical:

- Resistors/ceramic capacitors: Long axis horizontal (0° or 180°)

- **Reduces pick-and-place rotation movements (faster assembly)

DRC Integration: Layout design rules check component orientation, flag deviations for review. Ensures CPL reflects intentional design decisions, not layout accidents.

Fiducial Management

Global and Local Fiducials

Pick-and-place machines use fiducials—optical reference marks—for board alignment:

Global Fiducials: Board-level references (typically 3, non-collinear)

- Establish board coordinate system

- Correct for panel placement variation

- Standard position: corners, opposite board edges

Local Fiducials: Component-level references for high-precision parts

- QFN packages with 0.4mm pitch

- BGAs with fine-pitch balls

- Used for sub-pixel placement accuracy

CPL Integration: Fiducials included in CPL with special designation:

Designator: FID1, X: -45.0, Y: -30.0, Layer: Top, Comment: FIDUCIAL_GLOBAL

Designator: FID2, X: 45.0, Y: 30.0, Layer: Top, Comment: FIDUCIAL_GLOBAL

Machine recognizes fiducial markers, uses for optical alignment before component placement.

Fiducial Standardization

vBus Standard Positions: Carrier boards use consistent fiducial placement:

- Opposite corners, 5mm from board edges

- 1mm diameter copper circles, soldermask-free

- No silkscreen obstruction

Benefit: Manufacturers familiar with our fiducial conventions—less setup time, fewer alignment issues.

Panelization Considerations

Array Panel CPL

Production volumes often use panelized PCBs—multiple boards arranged in array on single panel:

CPL Array Generation: Script replicates master CPL for each panel position:

Panel layout: 2×3 array (6 boards)

Board spacing: 2mm between boards

Rail width: 5mm on panel edges

For each board position (i, j):

offset_x = i × (board_width + spacing) + rail_width

offset_y = j × (board_height + spacing) + rail_width

Generate CPL with offset applied to all coordinates

Designator Prefixing: Components in array receive position prefix:

Board 1: U1, C1, R1

Board 2: U1_2, C1_2, R1_2

Board 3: U1_3, C1_3, R1_3

Enables traceability during testing—if board 2 in panel fails, designators identify exact position.

Panel Fiducials

Panelized assembly requires panel-level fiducials:

- Located on panel rails (outside individual boards)

- Used for panel registration on conveyor

- Separate from individual board fiducials

CPL includes both panel and board fiducials with clear distinction.

Quality Assurance Integration

CPL Validation Scripts

Before sending CPL to manufacturer, automated validation:

Coordinate Sanity Checks:

- All X/Y coordinates within board outline?

- Components outside board boundary flagged (likely error)

Rotation Verification:

- Polarized components at standard orientations?

- Non-standard rotations flagged for manual review

Designator Cross-Check:

- Every schematic component has CPL entry?

- Every CPL entry matches schematic designator?

- Missing or extra entries flagged

Layer Verification:

- Components on appropriate layers?

- Through-hole components not in CPL? (hand-soldered or wave-soldered)

Validation Report: Generated automatically, reviewed before CPL release.

Visual Verification

CPL Preview Tool: Internal utility renders CPL visually:

- Component outlines drawn at specified coordinates

- Rotation shown with orientation indicator

- Overlays on PCB layout image for comparison

- Quick visual scan catches obvious placement errors

3D Assembly Preview: Modern EDA tools generate 3D assembly view from CPL:

- All components in position

- Rotation and orientation visible

- Mechanical interference check

- Validates CPL accuracy before manufacturing

Manufacturing Feedback Loop

Assembly House Integration

Manufacturers provide feedback on CPL quality:

Acceptance Testing: Assembly house imports CPL, reports issues:

- Format compatibility (did import succeed?)

- Coordinate accuracy (do components align with pads on actual board?)

- Rotation correctness (are polarized parts oriented correctly?)

First Article Inspection: Initial assembled board photographed, reviewed:

- Component placement accuracy validated

- Any rotation or position errors documented

- CPL corrections applied if needed

Continuous Improvement: Feedback incorporated into conversion scripts and component library metadata—issues corrected at source, not repeated.

Process Optimization

CPL data informs assembly optimization:

Component Grouping: Similar components (same package, same feeder) grouped in CPL sequence:

- Reduces feeder changes during assembly

- Speeds up placement cycle time

- Manufacturers can re-sequence if needed, but our optimization provides starting point

Nozzle Planning: Component heights inform nozzle selection:

- Tall components require specific nozzle types

- Grouping by height in CPL enables batch nozzle changes

- Reduces assembly interruptions

Metrics and Continuous Improvement

Key Performance Indicators

CPL First-Pass Acceptance Rate: Percentage of CPLs accepted by manufacturer without format corrections

- Target: 100% (vendor profile accuracy)

- Current: 98%+ (occasional edge cases with new vendors)

Placement Error Rate: Component placement errors per 1000 placements

- Industry average: 5-10 errors per 1000

- Our rate: <2 errors per 1000 (standardization reduces ambiguity)

Assembly Setup Time: Time from CPL receipt to production start

- Before standardization: 4-8 hours (manual data correction)

- After standardization: 30-60 minutes (machine programming only)

Automation ROI

Time Savings per Design:

- Manual CPL generation and correction: 3-5 hours per vendor

- Automated generation: 5 minutes per vendor

- Savings: 95% time reduction

Multi-Vendor Scalability:

- 4 vendors × 20 designs/year = 80 CPL deliveries

- Manual approach: 240-400 hours/year

- Automated approach: ~7 hours/year

- Savings: 230-390 engineering hours annually

Error Reduction:

- Fewer placement errors = fewer rework cycles

- Fewer assembly delays = faster time-to-market

- Higher first-pass yield = lower manufacturing costs

Conclusion: Standardization as Manufacturing Excellence

Pick-and-place standardization might seem like a mundane manufacturing detail, but it's fundamental infrastructure that enables our scaling strategy. By defining canonical CPL format, automating vendor-specific conversions, and integrating placement data into component libraries, we've transformed assembly data from source of delays into competitive advantage.

The results speak clearly: 98%+ first-pass CPL acceptance, <2 placement errors per 1000 components, 95% reduction in CPL preparation time, and seamless portability across global manufacturing partners. This isn't achieved through heroic manual effort—it's systematic engineering discipline applied to manufacturing data.

As our vBus ecosystem grows and we engage more manufacturing partners globally, our CPL standardization framework scales effortlessly. New vendors integrate in hours, not days. New designs generate correct assembly data automatically. Manufacturing quality remains consistently high regardless of production location.

This is manufacturing intelligence—where data standards, automation, and process discipline combine to create reliable, repeatable, scalable production capability. It's how we ensure that every Hoomanely product, regardless of where it's assembled, meets the same exacting quality standards from first board to ten-thousandth.