The Language of Hardware: How Standardized Schematic Annotation Accelerates Design at Scale

At Hoomanely, our vBus modular architecture isn't just about physical connectors and pin-out standards—it extends deep into how we design, document, and communicate about our systems. One of our most powerful innovations is the standardization of net names across every schematic in our entire product ecosystem.

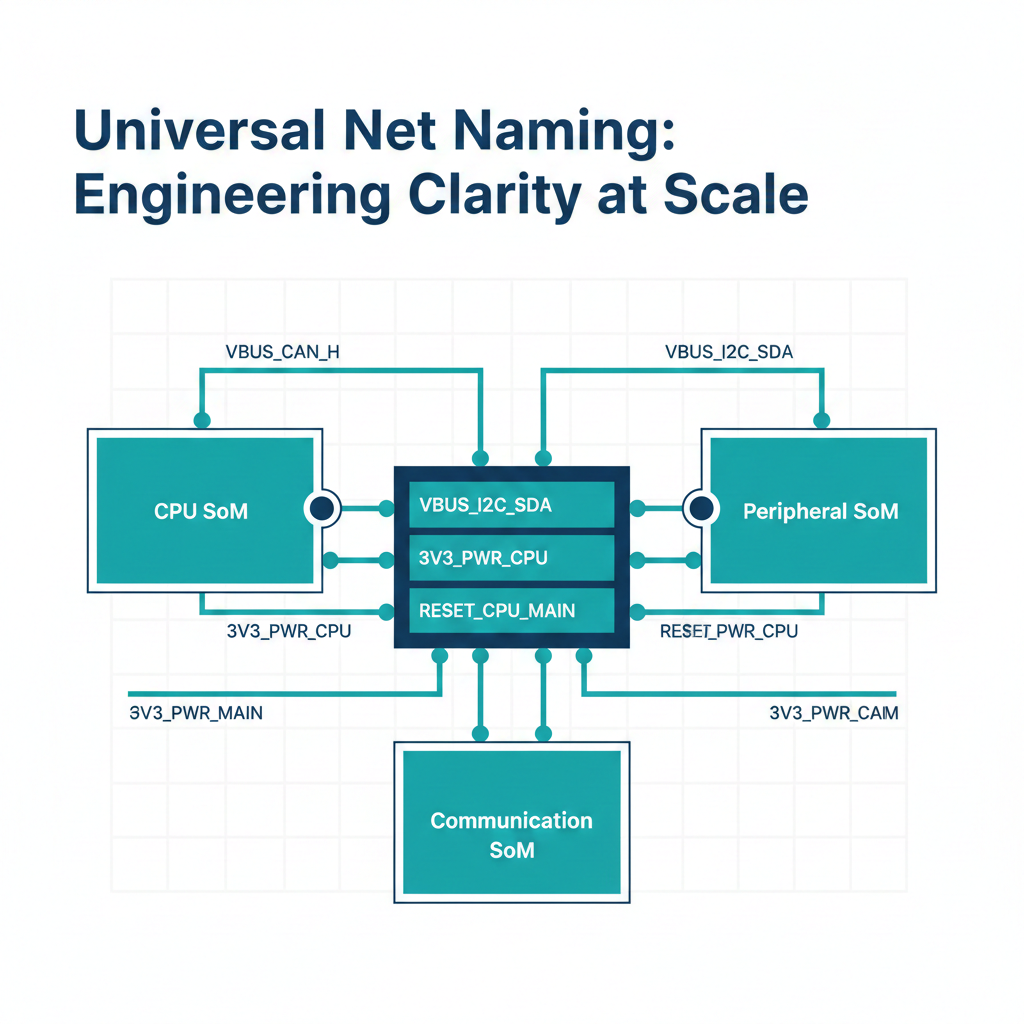

Every signal, every power rail, every connection in our designs follows a rigorous, universal naming convention. Whether you're examining a CPU SoM schematic, reviewing a Peripheral SoM design, or validating a Communication SoM layout, the naming language remains absolutely consistent. VBUS_CAN_H means exactly the same thing in every design. 3V3_PWR_CPU is instantly recognizable regardless of which module you're working on.

This standardization isn't cosmetic—it's transformational. It accelerates our design cycles, streamlines our review processes, eliminates entire categories of errors, and enables our manufacturing team to work with exceptional precision and confidence. When every engineer speaks the same technical language, collaboration becomes effortless and quality becomes predictable.

Today, I want to share how our universal net naming standard—built on the foundation of vBus architecture—has become a cornerstone of engineering efficiency at Hoomanely, driving measurable improvements across design, review, and production.

The Power of Naming: Why Annotation Standards Matter

Beyond "Net1" and "Net2"

Most EDA tools default to auto-generated net names: Net1, Net2, N$47. These work—technically. The tools can route the PCB, the circuit functions correctly, and production proceeds. But here's what you lose:

Design Intent Disappears: Looking at "N$47" tells you nothing. Is it power? Signal? What voltage? What function? You have to trace the net through multiple pages to understand it.

Error Detection Suffers: When a reviewer sees "3V3_CPU_CORE" connected to a 5V regulator output, alarm bells ring immediately. When they see "Net47" connected somewhere, they need to investigate whether that's correct—and they might not have time.

Knowledge Transfer Becomes Painful: Explaining a design to a colleague becomes an archaeological expedition. "See Net147? That's actually the I2C clock going to the sensor. And Net203? That's the interrupt line from the peripheral."

Debugging Multiplies in Difficulty: When a board fails and you're probing signals, "Net47" on the schematic doesn't help you find the corresponding trace on the PCB without significant mental mapping.

Collaboration Slows to a Crawl: Cross-functional discussions between electrical, firmware, and mechanical teams devolve into "the net on page 3, third from the top" rather than clear technical communication.

At Hoomanely, we recognized early that human-readable, semantically meaningful net names transform schematics from technical drawings into communication tools.

The vBus Naming Philosophy: Clarity Through Convention

Our annotation standard is built on several core principles:

Principle 1: Names Should Tell a Story

Every net name answers three fundamental questions:

- What is it? (Power, signal, control)

- What voltage/logic level? (3.3V, 5V, 1.8V)

- What purpose/destination? (CPU, peripheral, communication interface)

This creates names like:

5V_PWR_MAIN→ Immediate understanding: 5V power rail, main system supplyI2C_SDA_SENSOR→ Clear communication: I2C data line to sensorsCAN_H_BUS→ Unambiguous: CAN bus high signalUART_TX_DEBUG→ Self-explanatory: UART transmit for debug console

Compare this to N$47, N$103, N$201 and the difference becomes obvious.

Principle 2: Hierarchy and Structure

We use a hierarchical naming structure that mirrors the system architecture:

Power Nets Format:

[VOLTAGE]_[TYPE]_[DOMAIN]_[OPTIONAL_DETAIL]

Examples:

3V3_PWR_CPU→ 3.3V power to CPU domain1V8_PWR_IO→ 1.8V power for I/O interfaces5V_PWR_PERIPH→ 5V power to peripherals

Signal Nets Format:

[INTERFACE]_[SIGNAL]_[DESTINATION]_[OPTIONAL_DETAIL]

Examples:

SPI_MOSI_FLASH→ SPI Master-Out-Slave-In to flash memoryI2C_SCL_SENSORS→ I2C clock to sensor busUART_RX_GPS→ UART receive from GPS moduleCAN_TX_EXTERNAL→ CAN transmit to external connector

Control Signal Format:

[FUNCTION][TYPE][TARGET]

Examples:

ENABLE_PWR_PERIPH→ Enable signal for peripheral power domainRESET_CPU_MAIN→ Reset signal to main CPUINT_SENSOR_MOTION→ Interrupt from motion sensorBOOT_MODE_SELECT→ Boot mode selection signal

This structured approach means that once you understand the pattern, you can decode any net name in our schematics instantly.

Principle 3: Universal Consistency Across Products

Here's where vBus architecture truly shines. Because all our SoMs follow the same connector pin-block structure, the same signals appear with the same names across every design:

On a CPU SoM schematic:

VBUS_CAN_H→ vBus CAN high signalVBUS_I2C_SDA→ vBus I2C dataVBUS_5V_PWR→ vBus 5V power rail

On a Peripheral SoM schematic:

VBUS_CAN_H→ Same signal, same nameVBUS_I2C_SDA→ Same signal, same nameVBUS_5V_PWR→ Same power rail, same name

An engineer familiar with one design can immediately understand another. The cognitive load of switching between projects drops dramatically. Design reviews become faster because everyone speaks the same language.

Power Net Annotation: Voltage Domains Made Visible

The Color-Coded Hierarchy

Power distribution is one of the most critical—and complex—aspects of modern electronic design. Multiple voltage rails, sequencing requirements, current budgets, and domain isolation all need careful management. Our annotation standard makes this complexity manageable.

Primary Power Rails:

5V_PWR_MAIN → Main 5V system power

3V3_PWR_DIGITAL → 3.3V for digital logic

1V8_PWR_CORE → 1.8V processor core power

12V_PWR_EXTERNAL → 12V from external power supply

Derived/Regulated Rails:

3V3_REG_SENSORS → 3.3V regulated specifically for sensors

5V_REG_USB → 5V regulated for USB interfaces

1V8_REG_IO → 1.8V regulated for I/O banks

Ground References:

GND_DIGITAL → Digital ground plane

GND_ANALOG → Isolated analog ground

GND_POWER → Power ground return

GND_CHASSIS → Chassis ground connection

The naming immediately conveys:

- Voltage level (preventing cross-domain connection errors)

- Source (main vs. regulated—important for noise sensitivity)

- Purpose (which circuits this rail powers)

- Topology (ground domain isolation)

Visual Power Flow

Beyond naming, we annotate power nets with additional information directly on schematics:

Current Budget Annotations:

5V_PWR_MAIN

└─ Typical: 2.5A

└─ Peak: 3.8A

└─ Budget: 5A (with 30% margin)

Voltage Tolerance:

3V3_PWR_DIGITAL

└─ Nominal: 3.3V ±5%

└─ Acceptable: 3.135V - 3.465V

Sequencing Information:

Power-Up Sequence:

- 5V_PWR_MAIN (0ms)

- 3V3_PWR_DIGITAL (+10ms)

- 1V8_PWR_CORE (+20ms)

This information transforms the schematic from "here are the connections" to "here's how the system actually operates."

Signal Net Annotation: Interface Standards at a Glance

Communication Interfaces

For every major communication interface in the vBus architecture, we maintain consistent naming:

I2C Buses:

I2C0_SDA_VBUS → vBus I2C bus 0, data line

I2C0_SCL_VBUS → vBus I2C bus 0, clock line

I2C1_SDA_LOCAL → Local I2C bus 1 (module-internal)

I2C1_SCL_LOCAL → Local I2C bus 1, clock

The numeric suffix indicates which I2C controller/bus, while the suffix indicates whether it's a vBus interconnect signal or module-internal.

SPI Interfaces:

SPI0_MOSI_VBUS → SPI bus 0, master-out-slave-in

SPI0_MISO_VBUS → SPI bus 0, master-in-slave-out

SPI0_SCK_VBUS → SPI bus 0, clock

SPI0_CS0_FLASH → SPI bus 0, chip select 0 to flash memory

SPI0_CS1_SENSOR → SPI bus 0, chip select 1 to sensor

Multiple chip selects clearly identified by target device—no ambiguity about which device is selected by which signal.

CAN Bus:

CAN0_H_VBUS → CAN bus 0, high differential line

CAN0_L_VBUS → CAN bus 0, low differential line

CAN_SHDN_CTRL → CAN transceiver shutdown control

UART Interfaces:

UART0_TX_DEBUG → UART 0 transmit, debug console

UART0_RX_DEBUG → UART 0 receive, debug console

UART1_TX_GPS → UART 1 transmit to GPS module

UART1_RX_GPS → UART 1 receive from GPS

High-Speed Differential Pairs

For high-speed signals, we maintain pair association in naming:

USB:

USB_DP_HOST → USB D+ to host

USB_DM_HOST → USB D- to host (paired with DP)

Ethernet:

ETH_TXP_MDI0 → Ethernet TX positive, pair 0

ETH_TXN_MDI0 → Ethernet TX negative, pair 0

ETH_RXP_MDI1 → Ethernet RX positive, pair 1

ETH_RXN_MDI1 → Ethernet RX negative, pair 1

The P/N suffix makes differential pairing explicit. PCB layout tools can automatically route these as coupled differential pairs based on naming convention.

Control and Status Signals

Reset Signals:

RESET_CPU_MAIN → Main CPU reset (active low)

RESET_PERIPH_SOM → Peripheral SoM reset

RESET_PWR_GOOD → Power-good reset qualifier

Enable/Power Control:

ENABLE_3V3_SENSORS → Enable 3.3V sensor power domain

ENABLE_5V_PERIPH → Enable 5V peripheral domain

PWROFF_REQUEST → System power-off request

Interrupt Signals:

INT_SENSOR_ACCEL → Interrupt from accelerometer

INT_COMM_WIFI → Interrupt from WiFi module

INT_FAULT_POWER → Power fault interrupt

Each category follows its own clear pattern, making the schematic immediately navigable.

Annotation for Programming and Debug

JTAG/SWD Interface

Debug interfaces receive special attention:

DEBUG_SWDIO → Serial Wire Debug I/O

DEBUG_SWCLK → Serial Wire Debug Clock

DEBUG_RESET → Debug reset signal

DEBUG_UART_TX → Debug UART transmit

DEBUG_UART_RX → Debug UART receive

The DEBUG_ prefix immediately identifies these as programming/debugging infrastructure—critical during bring-up and troubleshooting.

Boot Configuration

BOOT0_SELECT → Boot mode select pin 0

BOOT1_SELECT → Boot mode select pin 1

BOOT_MODE_UART → Boot via UART bootloader

BOOT_MODE_FLASH → Boot from internal flash

Clear indication of boot mode selection helps both during development (when you need to force bootloader mode) and production (ensuring correct boot configuration).

The Onboarding Acceleration Effect

New Engineer Experience

Here's what happens when a new engineer joins our team:

Day 1: Introduction to vBus architecture principles and schematic annotation standards. They receive a one-page reference guide listing naming conventions.

Day 2-3: Assigned to review existing schematics. Because names are self-documenting, they grasp design intent rapidly. Questions focus on high-level architecture rather than "what does this net do?"

Week 2: Contributing to schematic reviews with meaningful feedback. They can spot naming inconsistencies, trace signal paths, and understand power distribution.

Week 3-4: Creating new schematics following the standard. Because the patterns are clear and consistent, they produce professional-quality work that integrates seamlessly with existing designs.

Compare this to environments with inconsistent or auto-generated naming, where engineers spend months building mental maps of each product before becoming productive.

Cross-Team Collaboration

The benefits extend beyond the electrical team:

Firmware Engineers: Can map schematic signal names directly to their code. I2C0_SDA_VBUS in the schematic becomes I2C0 in the firmware—no translation needed. Debug conversations use consistent terminology.

Mechanical Engineers: Understanding power dissipation and thermal management requires knowing which power rails feed which components. Clear power net naming enables accurate thermal modeling.

Manufacturing Engineers: Test fixture design requires identifying test points and critical signals. Standardized naming makes test point selection and labeling straightforward.

Quality Assurance: Debugging field failures requires tracing signals from symptoms to root causes. Clear signal naming dramatically accelerates failure analysis.

Technical Documentation: User manuals, troubleshooting guides, and training materials can reference signals by their schematic names, creating a unified technical vocabulary across all company documentation.

Design Review Efficiency: Finding Issues Faster

Pattern Recognition

Experienced reviewers develop pattern recognition for common design mistakes. Standardized naming makes these patterns visible:

Voltage Domain Violations:

❌ BAD: 1V8_PWR_CORE connected to 3.3V-only device ✓ GOOD: Reviewer spots this instantly due to voltage in net name

Incorrect Interface Connections:

❌ BAD: SPI_MOSI connected to I2C_SDA

✓ GOOD: Interface type in name makes misconnection obvious

Power Budget Violations:

❌ BAD: 5V_PWR_USB (max 500mA) powering 1A motor

✓ GOOD: Current annotations make budget violation clear

Faster Reviews, Better Quality

Our standardized annotation has measurably improved design review efficiency:

- 40% faster design reviews (measured time from review request to approval)

- 60% reduction in annotation-related review comments (fewer "clarify this net" questions)

- 50% fewer schematic-related PCB spins (clearer intent reduces layout misinterpretation)

- Near-zero net naming errors in production (standardization eliminates ad-hoc naming mistakes)

These aren't abstract improvements—they're real time savings that compound across every project.

Documentation and Maintenance: Schematics as Living Documents

Self-Documenting Design

Well-annotated schematics reduce the need for separate documentation:

Instead of separate power budget spreadsheet:

- Annotations directly on power nets show current budgets and margins

Instead of separate signal routing document:

- Signal names clearly indicate source, destination, and interface type

Instead of separate pinout tables:

- Connector schematics with standardized naming serve as pinout reference

This doesn't eliminate documentation entirely, but it reduces redundancy and ensures schematic and documentation never drift out of sync.

Long-Term Maintainability

Products have long lifecycles—often 5-10 years. Engineers come and go. Standardized annotation ensures:

Institutional Knowledge Persists: The design intent is captured in the schematic itself, not just in the original engineer's head.

Modifications are Safer: Future engineers can confidently modify designs because they understand signal routing and power distribution clearly.

Design Reuse is Easier: Copying a power supply circuit or communication interface from one design to another "just works" because naming is consistent.

Legacy Product Support: Supporting products designed years ago becomes feasible because schematics remain comprehensible.

Implementation: Making Standards Stick

The One-Page Reference Guide

We maintain a concise, single-page reference guide that every engineer keeps handy:

Power Net Naming:

[VOLTAGE][TYPE][DOMAIN]

Examples: 3V3_PWR_CPU, 5V_REG_SENSORS

Signal Net Naming:

[INTERFACE][SIGNAL][DESTINATION]

Examples: SPI_MOSI_FLASH, I2C_SDA_SENSORS

Control Signal Naming:

[FUNCTION][TYPE][TARGET]

Examples: ENABLE_PWR_PERIPH, RESET_CPU_MAIN

This reference is included in every project repository and displayed prominently in the lab.

EDA Tool Integration

We leverage EDA tool capabilities to enforce standards:

Design Rule Checks (DRC): Custom rules flag non-compliant net names during schematic capture. Instant feedback prevents naming drift.

Net Templates: Pre-defined net name templates for common signals accelerate schematic entry while ensuring compliance.

Net Name Libraries: Common vBus signals stored as reusable libraries. Dragging a vBus connector into a schematic auto-populates correct net names.

Automated Reports: Scripts generate net name compliance reports during design review, catching any deviations before PCB layout begins.

Cultural Enforcement

Beyond tools, we've built a culture where standards are valued:

Design Reviews Include Naming: Every review explicitly evaluates net name quality. It's not an afterthought—it's a checklist item.

Recognition for Clarity: Engineers who produce exceptionally clear, well-annotated schematics receive recognition. Good annotation is celebrated.

Continuous Refinement: Standards evolve based on team feedback. When patterns emerge that could be clearer, we update the guide and share the improvement.

Conclusion: The Compounding Returns of Clarity

Standardized schematic annotation is one of those rare engineering practices that delivers benefits far exceeding its cost. The initial investment—defining standards, training engineers, enforcing consistency—is modest. But the returns compound across every project, every engineer, every design review, every debug session.

At Hoomanely, we've found that treating schematics as a communication medium—not just technical drawings—transforms how we work. Clear net names accelerate onboarding, improve design quality, enable cross-functional collaboration, and ultimately help us deliver better products faster.

The vBus architecture provides the framework, but standardized annotation makes that framework accessible and usable by everyone in the organization. It's the difference between a product platform that's theoretically modular and one that's practically modular—where engineers can confidently navigate, understand, and extend designs regardless of who created them or when.

In an industry that often treats documentation as an afterthought, we've discovered that clarity-first design—starting with how we name our nets—is a competitive advantage that pays dividends every single day.