The Microcontroller Boot Journey: From Reset Vector to Main()

Introduction

Ever wondered what happens in those crucial milliseconds between powering on your smart device and seeing it spring to life? The journey from a cold hardware reset to a running application is one of the most fundamental processes in embedded systems—yet it remains invisible to most users.

Unlike desktop computers with complex BIOS systems, microcontrollers follow an elegant and deterministic boot sequence. This deep dive explores that complete boot process using real examples from an STM32H5-based system, revealing how hardware and software orchestrate reliable startup behavior in millions of IoT devices worldwide.

The Hardware Reset: Where It All Begins

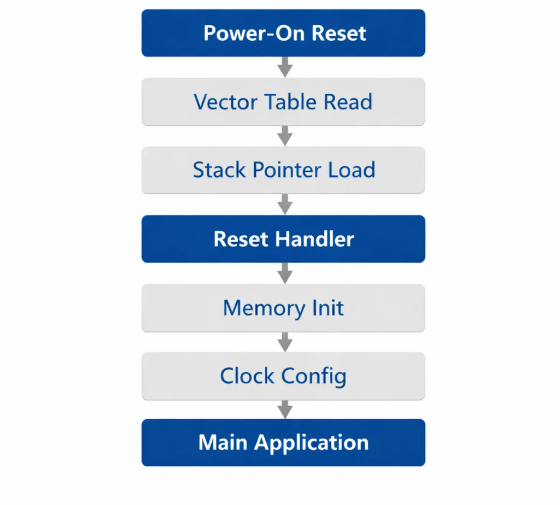

When power is first applied to a microcontroller, three critical hardware events occur in rapid succession.

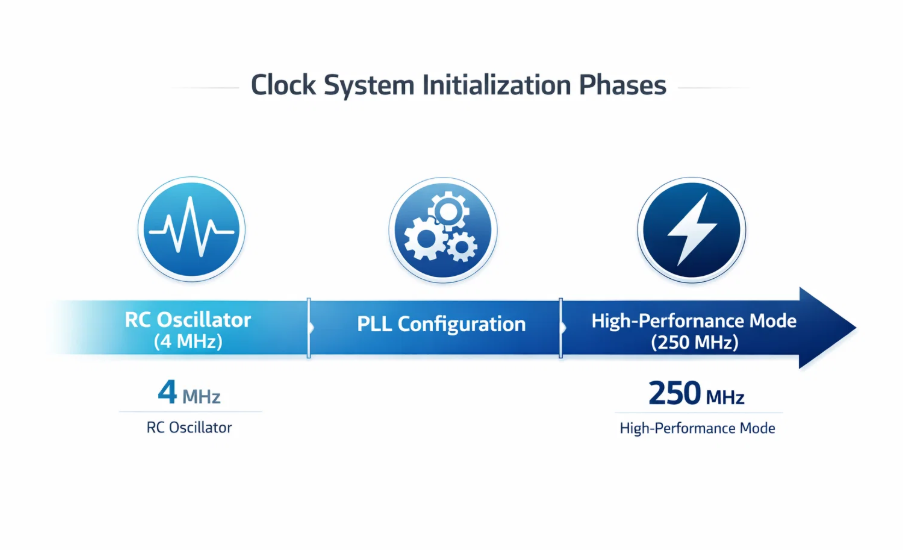

First, the power supply stabilizes, triggering internal voltage detectors. The STM32H5 series includes multiple power domains that must reach stable levels before any code execution begins. Next, the internal RC oscillator starts, providing a basic clock source. The system runs conservatively at 4MHz during this phase, ensuring reliable operation across temperature and voltage variations.

Finally, once stable, the Cortex-M33 core performs its first memory access—reading the reset vector from flash memory location 0x08000000. This single address contains everything the processor needs to begin executing code.

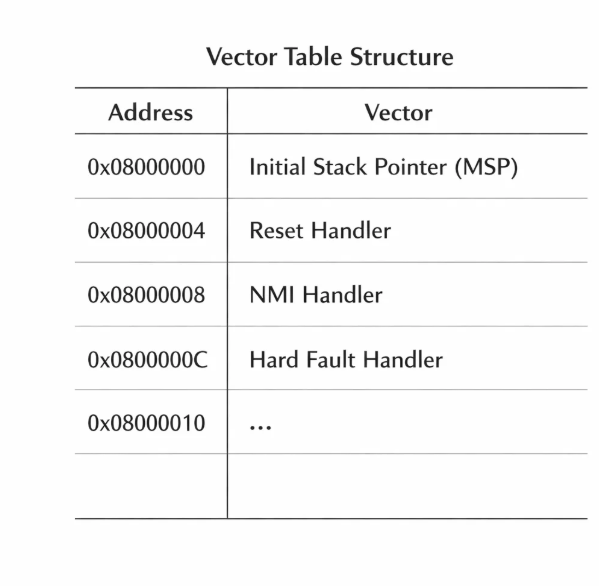

Vector Table: The System's Address Book

The vector table is the microcontroller's directory of critical addresses. Located at the very beginning of flash memory, it contains pointers to exception handlers and the initial stack pointer.

/* From startup_stm32h562xx.s */

g_pfnVectors:

.word _estack /* Initial Stack Pointer */

.word Reset_Handler /* Reset Handler */

.word NMI_Handler /* Non-Maskable Interrupt */

.word HardFault_Handler /* Hard Fault Handler */

The first two entries are critical. The Stack Pointer (MSP) points to the top of the main stack in RAM (0x20000000 + 640KB), while the Reset Handler Address identifies the first function to execute. This design ensures that even before any initialization code runs, the processor knows exactly where its stack is located and which function to call first.

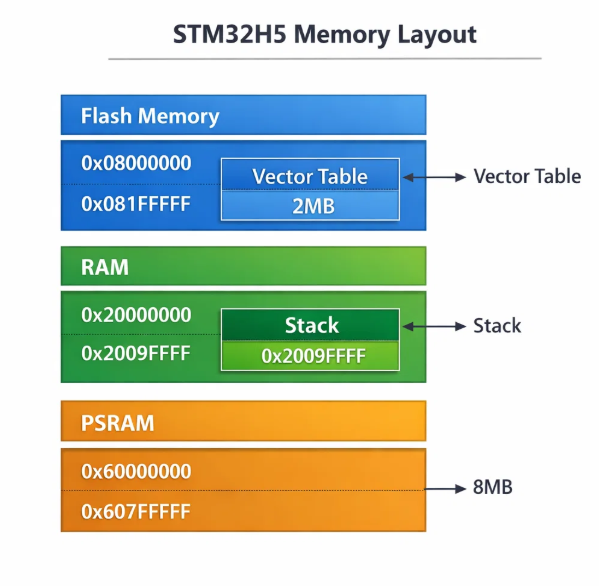

Memory Layout: The Foundation

The linker script defines the memory architecture that makes boot possible. Here's how memory regions are organized:

MEMORY

{

RAM (xrw) : ORIGIN = 0x20000000, LENGTH = 640K

FLASH (rx) : ORIGIN = 0x8000000, LENGTH = 2048K

PSRAM (xrw) : ORIGIN = 0x60000000, LENGTH = 8M

}

Flash holds read-only code and constants, including the vector table. RAM stores runtime data, stack, and heap for normal operation. PSRAM provides extended memory for large data buffers—critical for imaging applications like camera frame storage.

The linker script uses a KEEP directive to ensure the vector table always occupies the first bytes of flash memory where the hardware expects it, preventing optimization from inadvertently removing this critical structure.

The Reset Handler: System Initialization

The Reset Handler, written in assembly language, performs low-level initialization that cannot be done in C. It follows a precise sequence:

Stack Pointer Setup: Loads the main stack pointer from the first vector table entry, establishing the foundation for all function calls.

Data Initialization: Copies initialized variables from flash to RAM. Global variables with initial values like int counter = 42; exist as constants in flash and must be copied to RAM where they can be modified.

BSS Clearing: Zeros out uninitialized global variables, ensuring predictable behavior. All global variables declared without initializers start at zero, not random values.

Clock Configuration: Transitions from the conservative 4MHz RC oscillator to high-performance external crystals through PLL configuration, achieving target frequencies (250MHz for STM32H562).

C Runtime Setup: Prepares the environment for C code execution, including setting up the heap and initializing standard library support.

Multi-Stage Boot Architecture

Real embedded systems implement sophisticated multi-stage boot processes beyond basic hardware initialization.

Stage 1 validates hardware functionality—verifying external PSRAM, testing OCTOSPI flash communication, and validating bus transceivers. Stage 2 mounts the filesystem, initializing storage systems and validating integrity. Stage 3 starts application services like sensor interfaces and communication protocols.

This layered approach allows graceful degradation. If filesystem mounting fails, the device can still operate with reduced functionality while logging diagnostic information for troubleshooting.

Error Handling and Recovery

Modern embedded systems include sophisticated error handling during boot. Flash corruption detection validates critical code sections with checksums, enabling automatic recovery from backup regions. Clock failure triggers automatic fallback to the internal RC oscillator, allowing safe mode operation for diagnostic access.

Memory test procedures verify PSRAM functionality through pattern testing, while stack overflow detection and heap integrity checks prevent silent failures that could manifest later during operation.

Performance Optimization Strategies

Critical applications require fast boot times. Parallel initialization tackles multiple peripherals simultaneously, using DMA for memory operations during setup and overlapping filesystem mounting with hardware tests.

Selective feature enabling only initializes required peripherals, deferring non-critical setup until after the main application starts. Cache pre-loading fetches frequently used code into instruction cache before it's needed, reducing initial execution delays.

Strategic memory placement matters too. Boot code resides in the fastest flash regions, interrupt vectors align for optimal access, and the stack occupies the fastest RAM regions to minimize latency during critical operations.

Real-World Challenges

Temperature variations create interesting challenges. Cold starts extend RC oscillator stabilization time and increase flash memory access delays. Voltage fluctuations require brown-out detection during boot and graceful restart mechanisms on power interruptions.

Manufacturing testing validates boot sequence timing, detecting defects that affect startup reliability. Debug interfaces like JTAG/SWD must remain accessible during boot, with recovery mode entry mechanisms for field diagnostics.

Debugging the Boot Process

Common failures have distinctive signatures. Vector table corruption causes immediate hard faults or infinite reset loops—verify flash programming and protect critical regions. Stack overflow during initialization manifests as erratic behavior—monitor stack usage with a debugger and increase allocation if needed.

Clock configuration errors produce incorrect timing and peripheral malfunctions. These require verification of PLL settings and external crystal connectivity, with validation logic and fallback modes to maintain operation when primary clock sources fail.

At Hoomanely, we're building the future of preventive pet healthcare through continuous monitoring and early intervention. The boot process fundamentals described here directly enable our vision in several ways.

Reliable System Startup: Our pet health monitoring devices must boot consistently and predictably every time. Whether it's a sensor array monitoring vital signs or a camera system capturing behavioral patterns, reliable boot sequences ensure we never miss critical health indicators. This deterministic behavior forms the foundation of trustworthy pet healthcare technology.

Fast Response Times: Optimized boot sequences enable quick system recovery when devices restart, minimizing gaps in health monitoring. For continuous observation systems tracking parameters like temperature, activity levels, or respiratory patterns, every second of downtime represents lost health data. Efficient boot processes ensure maximum uptime.

Diagnostic Capabilities: Built-in boot-time diagnostics support remote monitoring of our device fleet. When a sensor node in a veterinary clinic reports boot issues, our cloud platform receives detailed diagnostic codes, enabling proactive maintenance before devices fail completely. This predictive approach extends device lifespan and ensures continuous care for pets.

The robust boot architecture scales from simple temperature sensors to complex multi-sensor fusion systems, providing the reliable foundation that Hoomanely's Physical Intelligence platform requires for seamless pet health monitoring.

Key Takeaways

Hardware-Software Integration: The boot process showcases elegant cooperation between hardware features (vector tables, memory controllers) and software design (linker scripts, initialization code) to create reliable system startup.

Deterministic Behavior: Unlike complex operating systems, microcontroller boot sequences follow predictable, repeatable patterns that enable real-time guarantees—essential for medical-grade pet monitoring devices.

Scalable Architecture: The same fundamental boot concepts apply whether building a simple sensor node or a complex imaging system, making these principles universally valuable for embedded developers.

Error Resilience: Modern boot sequences include comprehensive error detection and recovery mechanisms, ensuring system reliability even under adverse conditions like temperature extremes or power fluctuations.

Understanding this boot journey provides embedded developers with the knowledge to create robust, reliable systems that form the backbone of our increasingly connected world—and in Hoomanely's case, better health outcomes for our beloved pets.