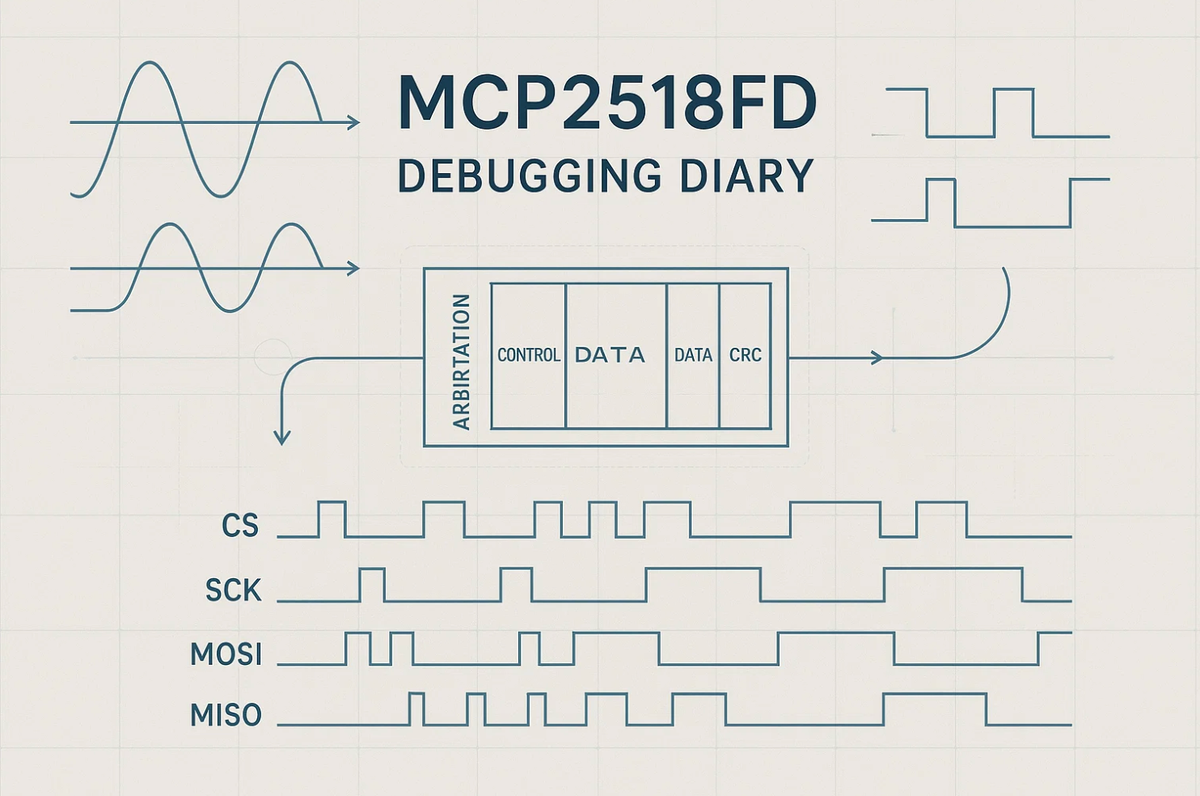

MCP2518FD Debugging Diary

The Microchip MCP2518FD is a popular external CAN-FD controller that interfaces with the host MCU over SPI. While the device performs well under controlled conditions, its field reliability is governed almost entirely by the quality of the host-side driver.

This article documents technical findings, failure signatures, and recovery patterns validated through lab testing focusing on SPI timing margins, interrupt consistency, and FIFO-level correctness guarantees.

These patterns contribute to a deterministic and fault-tolerant CAN-FD layer used inside distributed embedded systems such as those at Hoomanely.

1. Introduction

External SPI-based network controllers are conceptually simple: the MCU sends configuration commands, the controller manages the CAN-FD physical layer, and interrupts notify the MCU of events. In practice, the interaction boundary between SPI and the internal state machine of the MCP2518FD creates a narrow window where timing, synchronization, and FIFO transitions must align precisely.

During bring-up and stress testing, small deviations in timing or state sequencing can cause:

- inconsistent RX/TX state visibility

- incomplete or misaligned SPI responses

- premature interrupt assertion

- FIFO pointer drift

- stale frame reads

These behaviors do not indicate hardware defects they are typical of complex state machines exposed over SPI.

The objective of this article is to present a systematic driver design that remains correct even when communication timing shifts or FIFO state evolves rapidly.

2. Understanding the Real Integration Challenge

The MCP2518FD performs internal operations (CAN arbitration, bit timing logic, CRC verification, FIFO movement) asynchronously relative to the MCU’s SPI domain.

This asynchrony introduces three practical challenges:

Temporal Desynchronization

Internal controller state may change between two SPI transactions, even if those transactions happen back-to-back.

Partial Visibility Windows

Interrupt lines and registers do not always update atomically at the same moment.

This is not a flaw; it is inherent to any external peripheral with deeper internal FIFO structures.

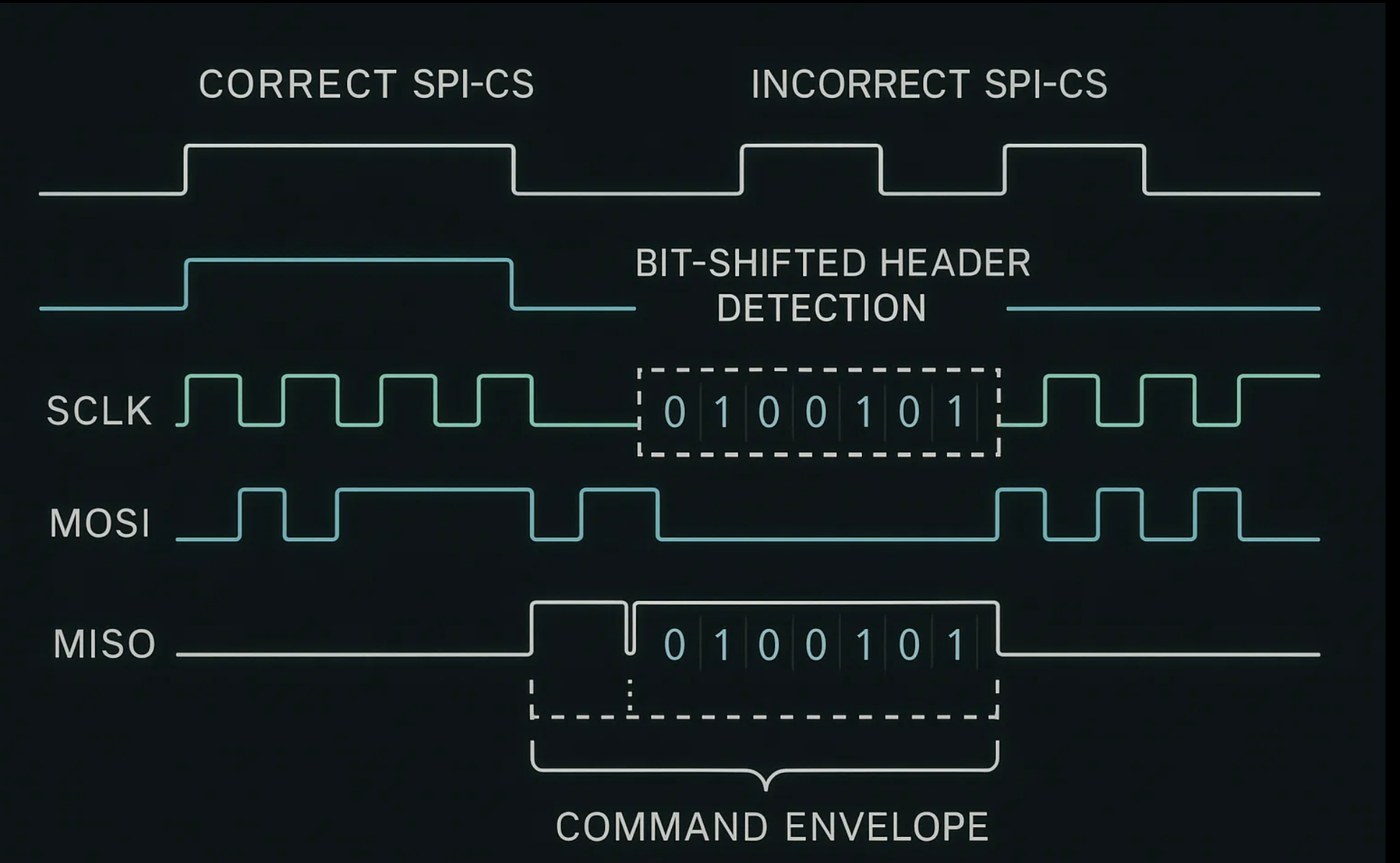

Burst-Read Sensitivity

SPI burst reads must respect boundaries defined by the controller. If the host violates these boundaries or underestimates CS timing requirements, the returned data may begin at an unexpected internal offset.

A robust driver must be designed to account for these behaviors as normal conditions.

3. SPI Timing — The Foundation of Reliability

SPI timing is the most deterministic layer in this system, yet it is also the most fragile when misconfigured.

Common issues arise from:

- insufficient CS setup time before the first SCK

- DMA-driven SPI that does not maintain strict CS sequencing

- MCU latencies that violate required inter-command spacing

- overly aggressive SPI frequencies without validating device margins

These lead to subtle forms of corruption—not full transfer failure, but:

- valid opcodes followed by invalid header bytes

- header bytes followed by misaligned payload bytes

- 0x00 / 0xFF patterns caused by misclocked first bits

3.1 Hardened SPI Transaction Envelope

A driver should encapsulate every transaction inside a strict envelope controlling:

- CS assertion timing

- transfer atomicity

- post-transfer validation

bool spi_transfer_hardened(const uint8_t *tx, uint8_t *rx, size_t len) {

gpio_clear(CS_PIN);

delay_cycles(CS_SETUP_CYCLES); // enforces minimum tCSS

bool status = spi_transfer_blocking(tx, rx, len);

gpio_set(CS_PIN);

// Sanity validation: MCP2518FD never uses 0x00 or 0xFF as valid header response

if (!status) return false;

if (rx[0] == 0x00 || rx[0] == 0xFF) return false;

return true;

}

This prevents the most common class of misalignment-induced failures.

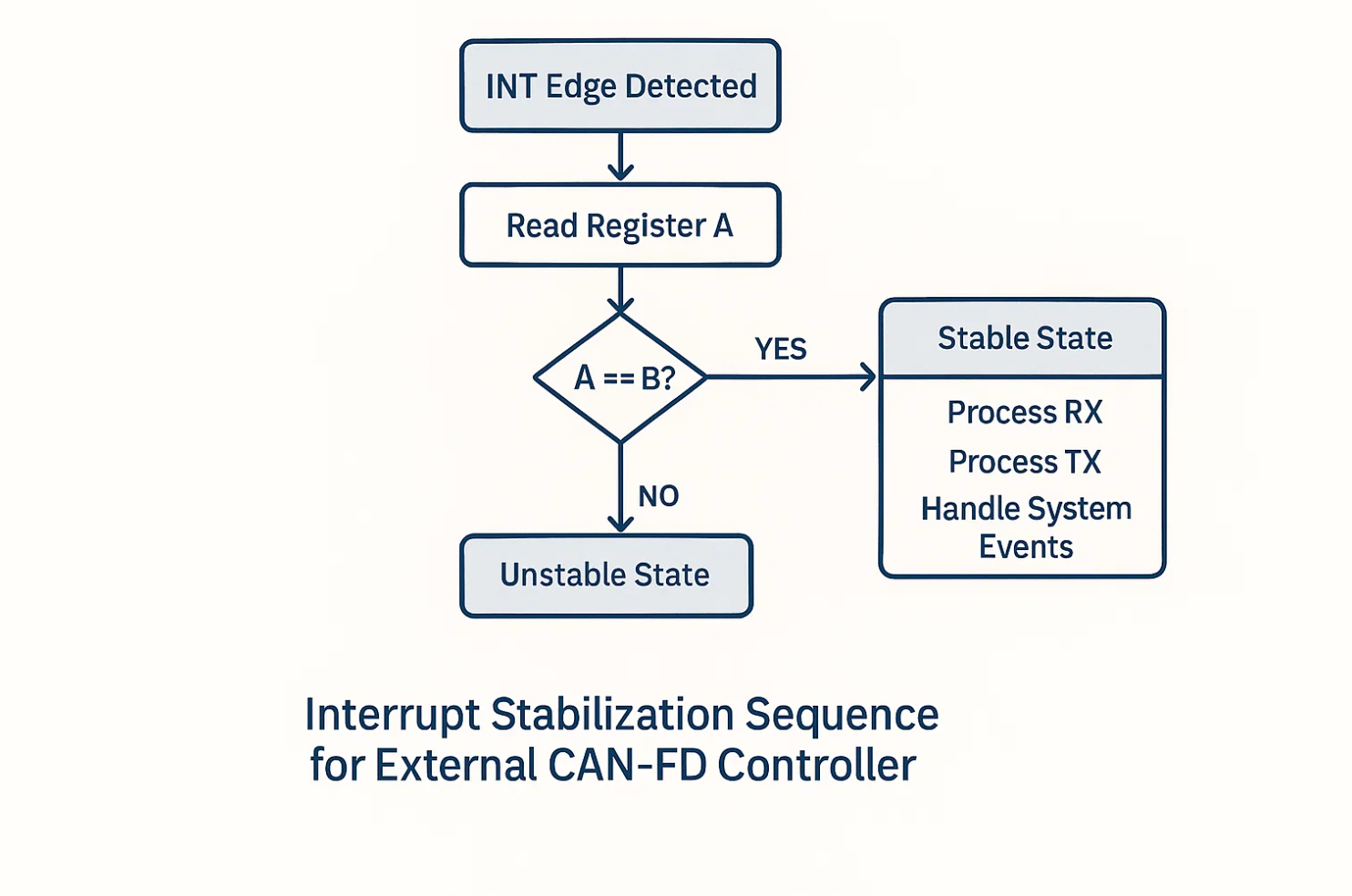

4. Interrupt Handling — Consistency Through Multi-Stage Validation

The MCP2518FD asserts an external INT pin when events occur, but the timing between:

- INT assertion

- status register update

- FIFO pointer movement

is not strictly simultaneous.

Therefore, reading the interrupt register once is not sufficient to confirm stability.

Inconsistencies between successive register reads indicate a transition window, not a fault. But the driver must handle these windows defensively.

4.1 Dual-Read Interrupt Stabilization

void mcp2518fd_handle_interrupt() {

uint32_t irq_a = read_reg(CAN_INT);

uint32_t irq_b = read_reg(CAN_INT);

if (irq_a != irq_b) {

// Indicates state is changing; safest action is FIFO boundary re-sync

reset_rx_tx_fifos();

return;

}

if (irq_a & RX_INT) handle_rx();

if (irq_a & TX_INT) handle_tx();

if (irq_a & SYS_INT) handle_system_events();

}

This method ensures the handler operates on stable state snapshots, preventing actions based on transient conditions.

5. RX Integrity: Every Frame Must be Proven Correct

A CAN-FD frame consists of several pieces of metadata (ID, flags, DLC, CRC) and the payload.

RX corruption is rarely total; more often, only the header or length field is wrong.

To prevent invalid frames from propagating upward, the RX pipeline must include:

- header integrity checks

- DLC-to-byte-length validation

- CRC verification (if applicable)

- FIFO index sanity checks

This ensures that only validated frames are exposed to higher layers.

5.1 Defensive RX Extraction Pattern

bool extract_rx_frame(can_frame_t *frame) {

uint8_t hdr[8];

if (!spi_transfer_hardened(cmd_read_rx_header, hdr, sizeof hdr))

return false;

uint8_t dlc = hdr[2] & 0x0F;

uint16_t expected_len = dlc_to_length(dlc);

if (expected_len > MAX_CANFD_PAYLOAD) return false;

uint8_t payload[64];

if (!spi_transfer_hardened(cmd_read_rx_payload, payload, expected_len))

return false;

if (!crc_validate(payload, expected_len))

return false;

assemble_frame(frame, hdr, payload);

return true;

}

This avoids accepting malformed frames due to subtle misreads.

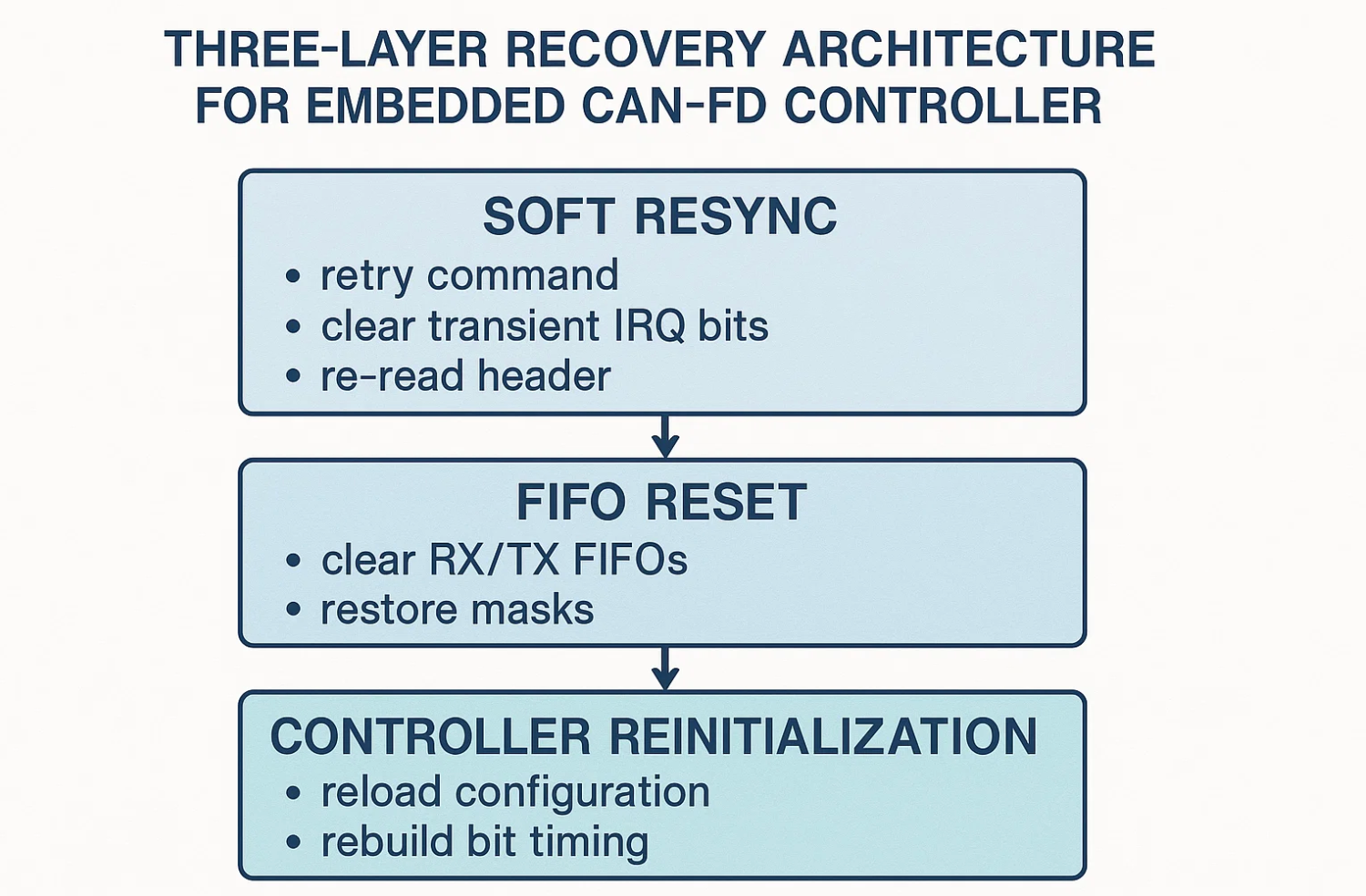

6. Deterministic Recovery Pipeline

Recovery is a structured escalation mechanism.

Instead of performing a full controller reset for every anomaly, a multi-layer approach preserves both uptime and determinism.

Soft Resynchronization

Used when:

- header inconsistency detected

- minor SPI misalignment suspected

Actions: - re-read header

- clear transient flags

- retry transaction

FIFO Reset

Used when:

- RX/TX pointers desynchronized

Actions: - clear FIFO

- restore masks

Full Reinitialization

Used when:

- repeated inconsistency persists

- interrupt state repeatedly unstable

Actions: - reconfigure controller

- rebuild timing parameters

This design ensures recovery is targeted, not destructive.

7. Applicability to Hoomanely’s Embedded Ecosystem

In Hoomanely’s architecture, devices interact across heterogeneous power domains, varying load patterns, and noise-prone consumer environments.

This makes bus-level determinism essential for:

- coordinated state between multiple sensor modules

- local inference nodes exchanging time-sensitive updates

- fault-tolerant orchestration of peripheral subsystems

- long-running systems where intermittent corruption can cascade

The patterns in this article are aligned with real-world deployment constraints—where reliability is not measured by ideal conditions, but by graceful handling of non-ideal ones.

By designing the MCP2518FD driver around verification, stability windows, and controlled recovery, communication integrity remains consistent despite fluctuating electrical or timing conditions.

Conclusion

The MCP2518FD is entirely capable of stable, deterministic CAN-FD operation, but only when paired with a host driver that accounts for:

- strict SPI envelope timing

- interrupt and register synchronization windows

- RX validation before acceptance

- structured recovery processes

This document captures engineering practices validated through lab testing and aligned with the operational realities of distributed embedded systems.

These techniques form the backbone of a reliable CAN-FD communication layer, supporting the deterministic behavior required across Hoomanely’s hardware ecosystem.